### Thermal and Power Sensing and Management for Mobile System-On-a-Chip

by Sofiane Chetoui

M.Sc., Brown University, Providence, RI, 2020 State Engineering Degree, M.Sc., Ecole Nationale Polytechnique, Algeria, 2017

> A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in School of Engineering at Brown University

> > PROVIDENCE, RHODE ISLAND

April 2022

© Copyright 2022 by Sofiane Chetoui

|      | is dissertation by Sofiane Chetoui is accepted in its present form<br>by School of Engineering as satisfying the<br>issertation requirement for the degree of Doctor of Philosophy. |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Recommended to the Graduate Council                                                                                                                                                 |

| Date |                                                                                                                                                                                     |

|      | Sherief Reda, Advisor                                                                                                                                                               |

| Date |                                                                                                                                                                                     |

| Date | Jacob Rosenstein, Reader                                                                                                                                                            |

| Date |                                                                                                                                                                                     |

|      | Ayse K. Coskun, Reader                                                                                                                                                              |

| Date |                                                                                                                                                                                     |

|      | Adel Belouchrani, Reader                                                                                                                                                            |

|      | Approved by the Graduate Council                                                                                                                                                    |

| Date |                                                                                                                                                                                     |

Andrew G. Campbell, Dean of the Graduate School

#### Vitae

Sofiane Chetoui was born in Tebessa, Algeria. He received his State Engineering Degree and M.Sc. in Electronics from Ecole Nationale Polytechnique, Algeria in 2017. He received his M.Sc. in Electrical and Computer Engineering from Brown University in 2020 during his studies in the Ph.D. program. His research aims to improve thermal behavior, energy efficiency and performance of mobile devices through runtime management. He is interested in thermal/power sensing, hardware characterization and modeling of modern Mobile SoCs. He uses control theory and machine learning to design the next generation of thermal and power management techniques. His research focuses as well on providing a better user-experience and battery lifetime management for Mobile Devices.

#### sofiane\_chetoui@brown.edu

Brown University, RI, USA

#### **Selected Publications:**

- S. Chetoui, M. Chen, A. Golas, F. Hijaz, A. Belouchrani, S. Reda, "Alternating Blind Identification of Power Sources for Mobile SoC", in Proceedings of the ACM/SPEC International Conference on Performance Engineering 2022.

- 2. S. Chetoui, R. Shahi, S. Abdelaziz, A. Golas, F. Hijaz, S. Reda, "ARBench: Augmented Reality Benchmark For Mobile Devices", under revision in IEEE Interna-

tional Symposium on Performance Analysis of Systems and Software (ISPASS) 2022.

- S. Chetoui, S. Reda, "Coordinated Self-tuning Thermal Management Controller for Mobile Devices", in IEEE Design Test. 2020 Feb 28;37(5):34-41.

- 4. S. Chetoui, S. Reda, "CasCon: Cascaded Thermal And Electrical Current Throttling for Mobile Devices", in IEEE Embedded Systems Letters. 2021 May 13.

- S. Chetoui, S. Reda, "Workload-and User-aware Battery Lifetime Management for Mobile SoCs", in 2021 IEEE Design, Automation Test in Europe Conference Exhibition (DATE) 2021 Feb 1 (pp. 1679-1684).

- M. Said, S. Chetoui, A. Belouchrani, S. Reda, "Understanding the sources of power consumption in mobile SoCs", in 2018 Ninth International Green and Sustainable Computing Conference (IGSC) 2018 Oct 22 (pp. 1-7). IEEE.

- Z. Yuan, P. Shukla, S. Chetoui, S. Nemtzow, S. Reda, AK. Coskun, "PACT: An extensible parallel thermal simulator for emerging integration and cooling technologies", in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems. 2021 May 11.

- 8. Z. Yuan, P. Shukla, S. Chetoui, C. Knox, S. Nemtzow, S. Reda, AK. Coskun, "Towards Fast and Accurate Parallel Chip Thermal Simulations with PACT".

#### Acknowledgements

This thesis would not have been possible without the constant support, guidance and inspirations of many kind individuals. First and foremost, I would like to express my immense gratitude to my advisor and mentor, Prof. Sherief Reda, whose guidance, support, and valuable insights during the course of my research has made this thesis possible.

I would also like to thank Prof. Jacob Rosenstein, Prof. Ayse K. Coskun and Prof. Adel Belouchrani for being on my defense committee and taking the time to review my thesis.

I am extremely thankful for the productive collaborations with all my co-authors, Prof. Adel Belouchrani, Prof. Ayse K. Coskun, Prof. Mostafa Said, Dr. Zihao Yuan, Abhinav Golas, Farrukh Hijaz, Andey Donzelli, Michael Chen, Rahul Shahi, my advisor Prof. Sherief Reda, and many others. My work would not have been possible without them. Specifically, I would like to sincerely thank Prof. Adel Belouchrani for his valuable insights and guidance.

I would like to thank Samsung SARC for giving me internship opportunities twice. Especially, I would like to thank Can Hankendi for his distinguished mentorship. I would like to thank the Power Methodology team at Nvidia for giving me an amazing internship opportunity, more specifically, I would like to thank Kapil Dev for his distinguished mentorship and guidance. I would also like to thank my fellow graduate students and friends at Prof. Reda's group at Brown: Reza Azimi, Soheil Hashimi, Hokchhay Tran, Abdelrahman Hosny, Farnaz Nouraei, Marina Hesham, Jingxiao Ma, Ahmed Agiza and many others for always making the last five years memorable.

I would like to express my immense gratitude to Ghania Rais for her great care and for being a one-of-a-kind teacher to me. I am greatly thankful for Mohamed Saoudi for his advice and support during and after my high school studies. I would like to express my deep gratitude for Noureddine Tayebi for his support and help before and during my PhD track.

I would like to thank Hala Lemmouchi for the years of support, encouragements, and many unforgettable memories.

Last but not least, I would like to thank my parents, M. Larbi Chetoui and Leila Chamekh, and my siblings for their unwavering support and love. I have learned a lot from them. Without them, none of what I achieved today would be possible. Abstract of "Thermal and Power Sensing and Management for Mobile System-On-a-Chip" by Sofiane Chetoui, Ph.D., Brown University, April 2022

Mobile devices became an essential part of daily life with the increased computing capabilities and features. The leaps that Mobile System-On-a-Chip (SoC) have taken in the past decade led to an explosive growth of mobile devices. Mobile SoCs have become the leading product in the semiconductor industry, due to its continually improving performance and decreasing cost. Their designs have rapid evolution, at least a new design is released each year, and new designs tend overshadow the older ones. Technology scaling, heterogeneous multiprocessor designs and the integration of specialized hardware units are among the main factors enabling the performance increase. This increase has enabled new applications that require intensive computation, raise critical thermal, power and energy constraints. Elevated chip temperatures and power density substantially affect the user experience due to performance throttling and decreased battery lifetime.

This thesis aims at improving the performance and the battery lifetime of mobile devices through thermal and power sensing and management, under thermal, power and energy constraints. On the sensing side, this thesis first introduces an Alternating Blind Identification of Power sources (Alternating-BPI), a technique that accurately estimates the power consumption of individual SoC units without the use of any design based models. The proposed technique uses a novel approach to blindly identify the sources of power consumption, by relying only on the measurements from the embedded thermal sensors and the total power consumption. Additionally, on the sensing side we propose a Deconvolutional Neural Network (DCNN) based power map estimation. The proposed approach relies only on the usage of the few available embedded thermal sensors on the SoC to estimate the full SoC power map. Afterwards, the thesis tries to take a step towards the improvement of the Augmented Reality mobile experience by performing a power and hardware characterization of Augmented Reality Applications. The characterization includes designing and developing ARBench, an augmented reality benchmark for mobile devices. The benchmark and the Alternating-BPI technique were used to study the performance and power trade-offs of different CPU multi-core configurations, in order to provide insights to save power while meeting the AR performance requirements. On the runtime management side, this thesis proposes a coordinated self-tuning thermal management controller on the basis of online deep learning that continuously adapts to characteristics and operating conditions, while taking into account both skin temperature and junction temperature constraints in a coordinated manner. We also propose a cascaded controller for mobile devices that controls the different sources of current and thermal emergencies in a coordinated manner. The controller design was inspired from the physical relations that exist among the different current and thermal measures, and it allows to achieve better performance while saving power. Finally, this thesis introduces a novel workload- and user-aware battery lifetime management technique that maximizes the performance under the user's desired battery lifetime. Our approach leverages insights about the running workloads by collecting CPU-GPU performance counters, which are used to proactively scale the CPU-GPU frequencies using machine learning.

# Contents

| Vi | itae                                                              | iv |

|----|-------------------------------------------------------------------|----|

| A  | cknowledgments                                                    | vi |

| 1  | Introduction                                                      | 1  |

|    | 1.1 Problem Characterization                                      | 1  |

|    | 1.2 Major Thesis Contributions                                    | 3  |

| 2  | Background                                                        | 11 |

|    | 2.1 Thermal and power sensing                                     | 11 |

|    | 2.2 Thermal and power runtime management                          | 14 |

|    | 2.3 Energy and battery lifetime management                        | 17 |

| 3  | Alternating Blind Identification of Power Sources for Mobile SoCs | 19 |

|    | 3.1 Motivation                                                    | 21 |

|    | 3.2 Alternating Blind Identification of Power sources             | 22 |

|    | 3.2.1 The proposed approach                                       | 22 |

|    | 3.2.2 The Alternating-BPI tool                                    | 26 |

|    | 3.3 Experiments and Results                                       | 29 |

|    | 3.3.1 Experimental setup                                          | 29 |

|    | 3.3.2 Results                                                     | 32 |

|    | 3.4 Conclusion                                                    | 41 |

| 4 | Dec | onvolutional Neural Network Based Power Map Estimation                  | 43 |

|---|-----|-------------------------------------------------------------------------|----|

|   | 4.1 | Motivation                                                              | 44 |

|   | 4.2 | Deconvolutional Neural Network Based Power Map Estimation               | 45 |

|   | 4.3 | Experiments and Results                                                 | 49 |

|   |     | 4.3.1 Experimental setup                                                | 49 |

|   |     | 4.3.2 Results                                                           | 51 |

|   | 4.4 | Conclusion                                                              | 52 |

| 5 | Pow | er and Hardware Characterization for Augmented Reality Applications     | 55 |

| 5 | 100 | er and Hardware Characterization for Augmented Reality Applications     | 55 |

|   | 5.1 | Motivation                                                              | 56 |

|   | 5.2 | Experimental setup                                                      | 58 |

|   | 5.3 | Hardware utilization and power characterization of mobile AR apps       | 59 |

|   | 5.4 | Augmented Reality Benchmark                                             | 65 |

|   | 5.5 | AR Benchmarking of Commercial Mobile Devices                            | 70 |

|   | 5.6 | Phase analysis of AR workloads                                          | 73 |

|   | 5.7 | Performance and Power evaluation of different CPU multi-core configura- |    |

|   |     | tions                                                                   | 77 |

|   | 5.8 | Conclusion                                                              | 80 |

| 6 | Coo | rdinated Self-tuning Thermal Management Controller for Mobile Devices   | 82 |

|   | 6.1 | Motivation                                                              | 83 |

|   | 6.2 | Proposed self-tuning methodology for thermal management                 | 85 |

|   | 0.2 |                                                                         |    |

|   |     | 6.2.1 Proposed self-tuning Controller for junction temperature          | 85 |

|   |     | 6.2.2 Proposed coordinated junction & body self-tuning controller       | 87 |

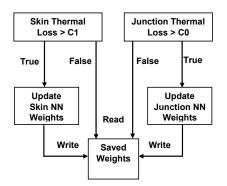

|   |     | 6.2.3 Efficient online Learning                                         | 89 |

|   | 6.3 | Experiments and results                                                 | 90 |

|   |     | 6.3.1 Experimental setup                                                | 90 |

|   |     | 6.3.2 Results                                                           | 91 |

|          | 6.4  | Conclusion                                                         | 96  |

|----------|------|--------------------------------------------------------------------|-----|

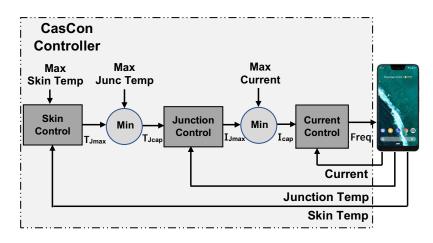

| 7        | Cas  | Con: Cascaded Thermal And Electrical Current Throttling for Mobile |     |

|          | Dev  |                                                                    | 97  |

|          | 7.1  | Motivation                                                         | 98  |

|          | 7.2  | Proposed CasCon controller                                         | 100 |

|          |      | 7.2.1 The electrical current controller                            | 101 |

|          |      | 7.2.2 The junction temperature controller                          | 102 |

|          |      | 7.2.3 The skin temperature controller                              | 102 |

|          | 7.3  | Results and Experimental Setup                                     | 103 |

|          |      | 7.3.1 Experimental setup                                           | 103 |

|          |      | 7.3.2 Results                                                      | 105 |

|          | 7.4  | Conclusion                                                         | 107 |

| 8        | Wor  | kload- and User-aware Battery Lifetime Management for Mobile SoCs  | 109 |

| -        | 8.1  | Motivation                                                         | 110 |

|          |      |                                                                    | -   |

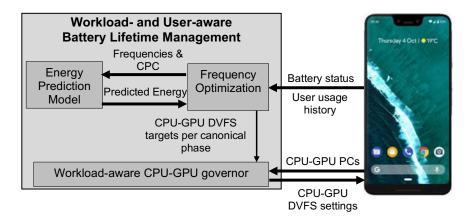

|          | 8.2  | Proposed work                                                      | 112 |

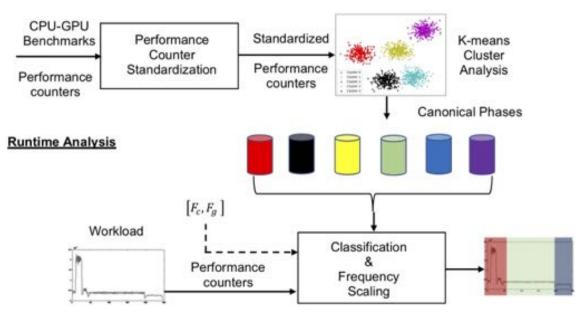

|          |      | 8.2.1 Workload-aware governor                                      | 112 |

|          |      | 8.2.2 Energy prediction model                                      | 114 |

|          |      | 8.2.3 Frequency optimization                                       | 115 |

|          | 8.3  | Experiments and results                                            | 118 |

|          |      | 8.3.1 Experimental setup                                           | 118 |

|          |      | 8.3.2 Results                                                      | 118 |

|          | 8.4  | Conclusion                                                         | 124 |

| 9        | Sum  | mary and Possible Extensions                                       | 126 |

| <u>۲</u> |      | Summary of the Dissertation                                        | -   |

|          | 9.1  |                                                                    | 127 |

|          | 9.2  | Possible Research Extensions                                       | 129 |

|          | Bibl | iography                                                           | 130 |

# **List of Figures**

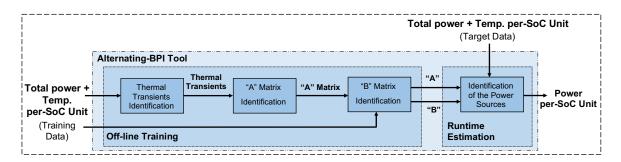

| 3.1 | The Alternating-BPI tool.                                                                                                                           | 27 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

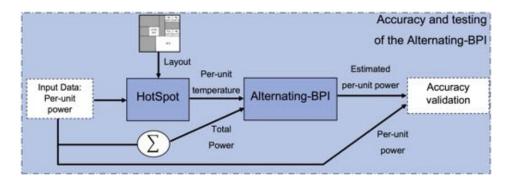

| 3.2 | The verification and testing flow of the Alternating-BPI.                                                                                           | 29 |

| 3.3 | Layout of the big.LITTLE+GPU SoC [43] used for the testing of the Alternating-BPI.                                                                  | 30 |

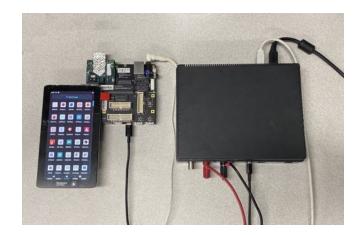

| 3.4 | The used setup for the experimental verification of Alternating-BPI: the 865-HDK on the left side, and the Monsoon power monitor on the right side. | 32 |

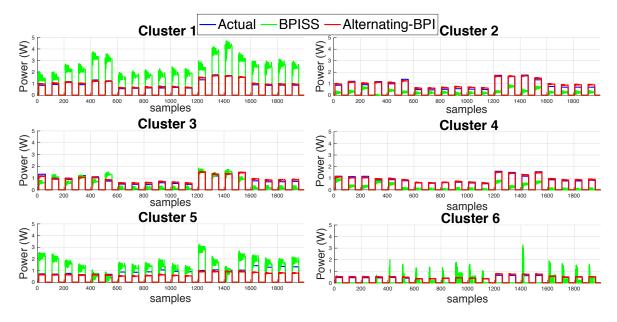

| 3.5 | The accuracy of BPISS vs Alternating-BPI in predicting the power per-<br>cluster for the big.LITTLE+GPU floorplan.                                  | 34 |

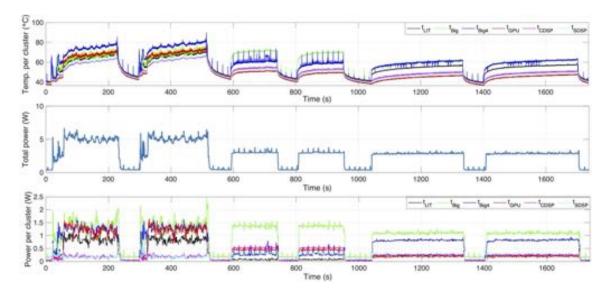

| 3.6 | The Alternating-BPI estimated power per-SoC Unit of the Snapdragon-      865.                                                                       | 36 |

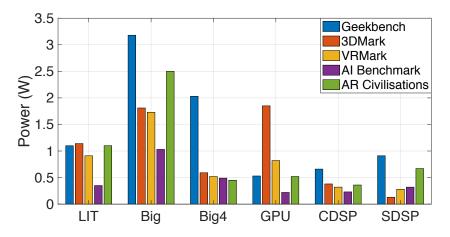

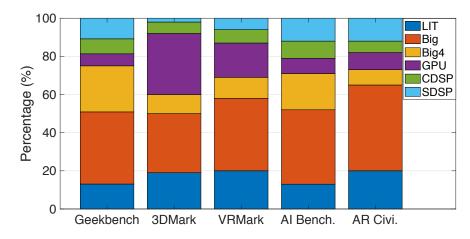

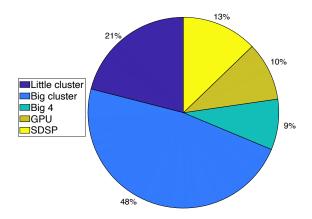

| 3.7 | The Alternating-BPI estimated power per-SoC Unit of the Snapdragon-         865 for the benchmarking apps.                                          | 38 |

| 3.8 | The Alternating-BPI estimated percentage power consumption of per-SoC<br>Unit of the Snapdragon-865 for the benchmarking apps.                      | 39 |

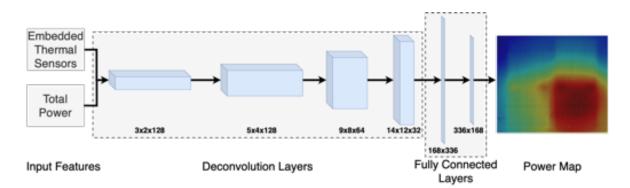

| 4.1 | The offline training flow of the DCNN based power map estimation                                                                                    | 46 |

| 4.2 | The neural network architecture of the proposed DCNN based power map                                                                                |    |

|     | estimation.                                                                                                                                         | 47 |

| 4.3 | The used FLIR SC5000 Series thermal camera setup.                                                                                                   | 49 |

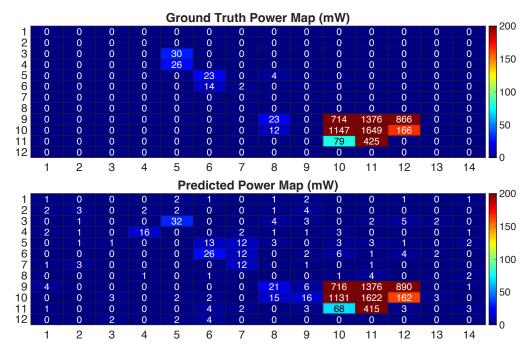

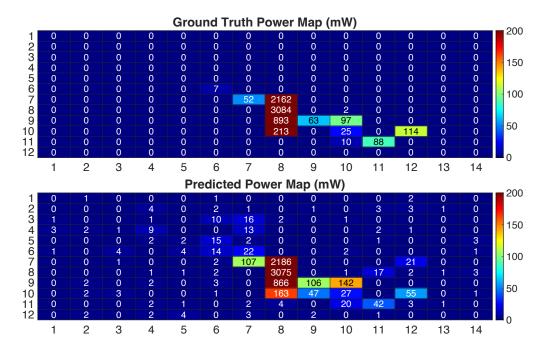

| 4.4 | The ground truth power map vs the predicted power map by the proposed                                                                               |    |

|     | work for the Face Detection benchmark.                                                                                                              | 53 |

| 4.5 | The ground truth power map vs the predicted power map by the proposed work for the Speech Recognition benchmark.                                    | 53 |

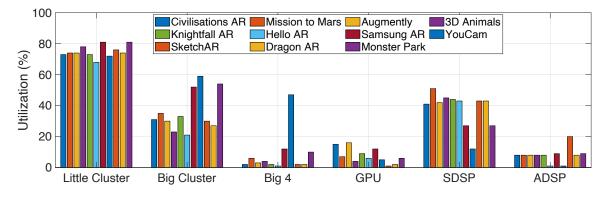

| 5.1 | Per-Hardware unit utilization of different AR Apps running on the Snap-                                                                             |    |

|     | dragon 865 SoC                                                                                                                                      | 61 |

| 5.2 Per-Hardware unit power consumption of Civilisations           | AR on the Snap-           |    |

|--------------------------------------------------------------------|---------------------------|----|

| dragon 865 SoC                                                     |                           | 62 |

| 5.3 Per-AR process power consumption of Civilisations AR of        | on the Snapdragon         |    |

| 865 SoC.                                                           |                           | 65 |

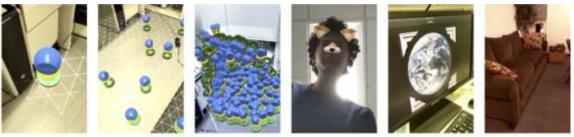

| 5.4 Outputs of the six benchmarks of the ARBench                   |                           | 68 |

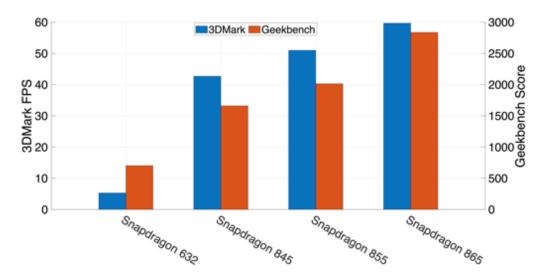

| 5.5 3DMark and Geekbench performance numbers on diffe              | erent Snapdragon          |    |

| SoCs                                                               | · · · · · · · · · · · · / | 70 |

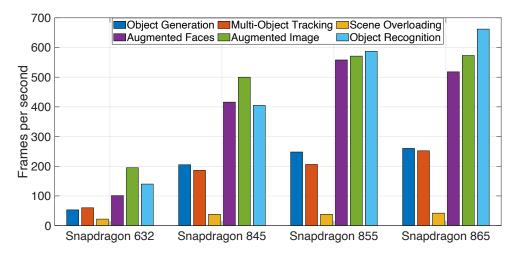

| 5.6 The per-benchmark AR performance of different Snapdr           | ragon SoCs while          |    |

| running the proposed benchmark                                     |                           | 71 |

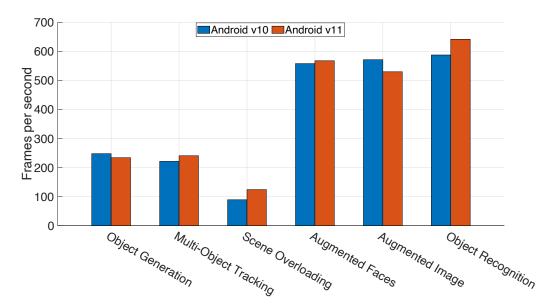

| 5.7 The per-benchmark AR performance of Android v10 a              | and Android v11           |    |

| while running the proposed benchmark.                              |                           | 72 |

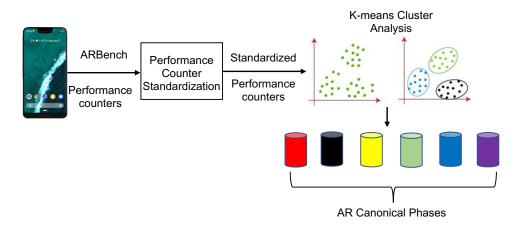

| 5.8 The phase analysis methodology.                                | ,                         | 73 |

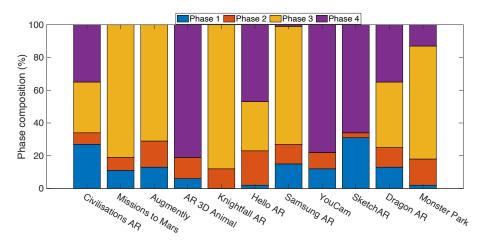

| 5.9 The canonical phase composition of different AR apps.          | , ,                       | 77 |

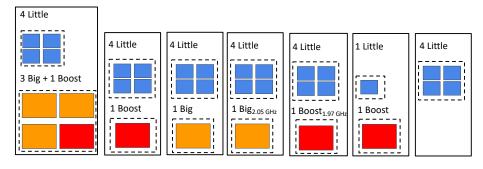

| 5.10 The different CPU multi-core configurations for which         | the performance           |    |

| and power trade-off is analyzed using ARBench                      | ,                         | 78 |

| 5.11 The per-benchmark AR performance of the different CP          | U multi-core con-         |    |

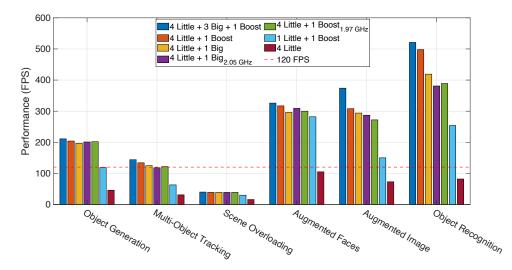

| figurations as reported by ARBench.                                |                           | 79 |

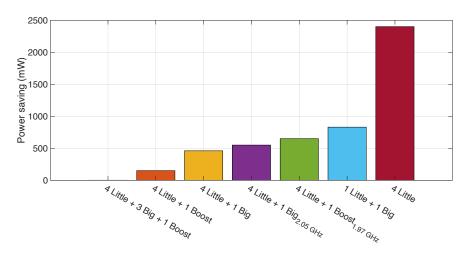

| 5.12 The power savings of the different CPU multi-core config      | gurations as to the       |    |

| default configuration.                                             |                           | 80 |

|                                                                    |                           |    |

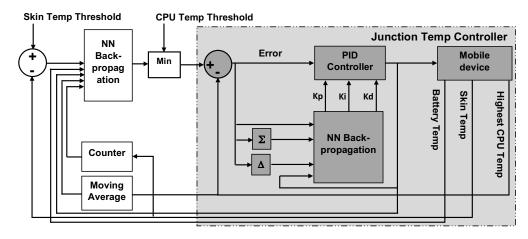

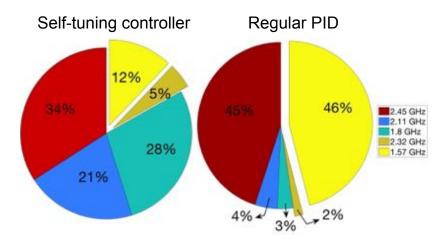

| 6.1 Coordinated self-tuning controller scheme to manage            | 0                         | 06 |

| temperature and the skin temperature                               |                           | 86 |

| 6.2 Neural Network Update Mechanism.                               |                           | 89 |

| 6.3 Frequency distribution of the self-tuning controller com       | pared to the regu-        |    |

| lar PID while running Geekbench 25 benchmarks                      |                           | 95 |

|                                                                    |                           |    |

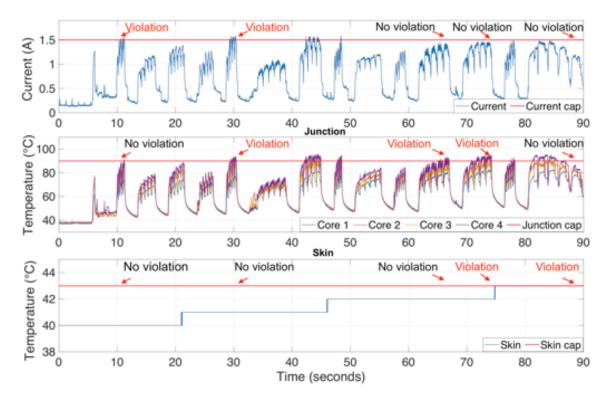

| 7.1 The electrical current and thermal traces while running Geekbe | ench on the Google        |    |

| 2 XL                                                               |                           | 99 |

| 7.2 Proposed coordinated thermal and electrical current controller | 10                        | 00 |

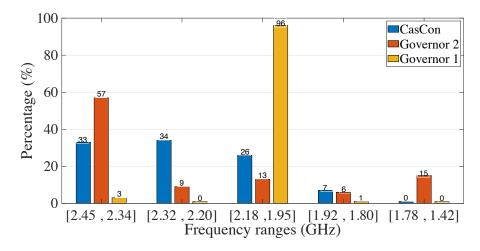

| 7.3 Time spent on each frequency range by the different governor   | s 10                      | 05 |

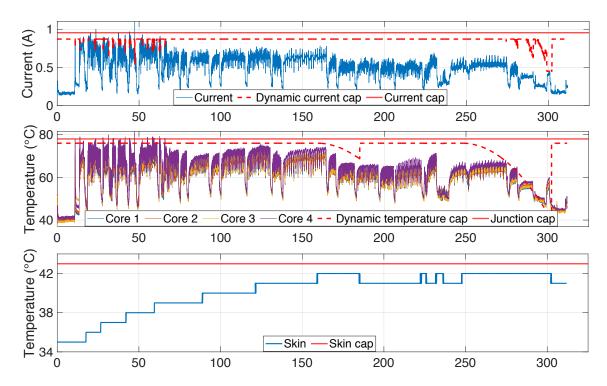

| 7.4 CasCon : run-time dynamic electrical current and temperature   | e capping 10              | 08 |

| 8.1 Workload- and User-aware Battery Lifetime Management.          | 1                         | 12 |

| 8.2 | Workload-aware governor.                      | 113 |

|-----|-----------------------------------------------|-----|

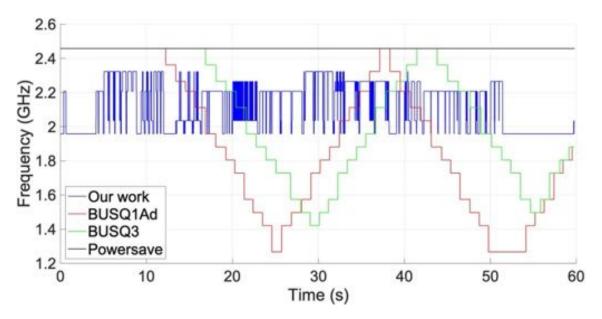

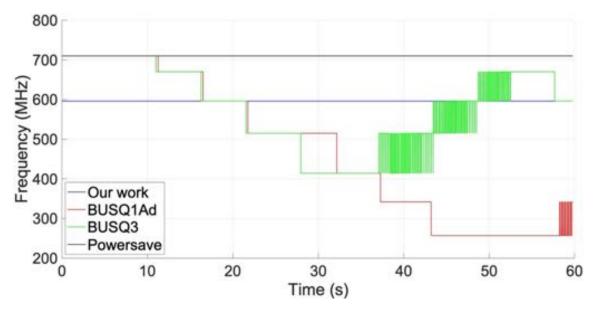

| 8.3 | CPU frequency traces while running Geekbench. | 120 |

| 8.4 | GPU frequency traces while running 3DMark.    | 122 |

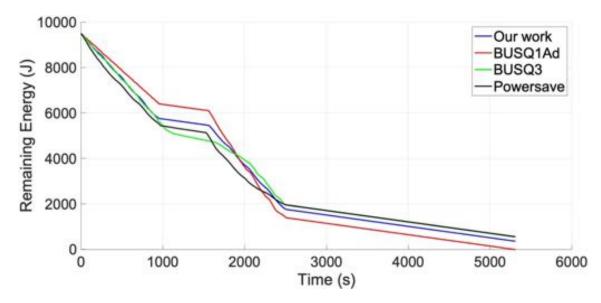

| 8.5 | Discharge profile.                            | 122 |

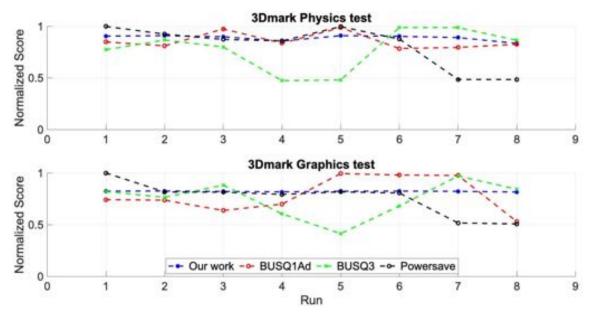

| 8.6 | QoS variation using 3DMark.                   | 124 |

# **List of Tables**

| 3.1 | The power estimation error of the Alternating-BPI against BPI and BPISS     |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | using three floorplan benchmarks.                                           | 32  |

| 3.2 | The hardware blocks composition of each cluster.                            | 35  |

| 3.3 | The clusters used by the set of benchmarking apps.                          | 37  |

| 4.1 | DCNN parameters used in this work.                                          | 48  |

| 4.2 | The different benchmarks used to evaluate the accuracy of the proposed      |     |

|     | work.                                                                       | 50  |

| 4.3 | The accuracy of the power map estimation of the proposed work using the     |     |

|     | training and testing data sets.                                             | 51  |

| 4.4 | The per-benchmark accuracy of the power map estimation of the proposed      |     |

|     | work.                                                                       | 52  |

|     |                                                                             |     |

| 5.1 | The set of Augmented Reality Apps used for the hardware characterization.   | 60  |

| 5.2 | The description and the objective of each benchmark of ARBench              | 67  |

| 5.3 | The normalized average performance counter values for each AR canoni-       |     |

|     | cal phase.                                                                  | 74  |

| 5.4 | The canonical phase composition of the ARBench benchmarks                   | 75  |

| 6.1 | Thermal evaluation of the implemented junction temperature controllers.     | 91  |

|     |                                                                             |     |

| 6.2 | Performance and thermal evaluation of the implemented controllers           | 94  |

| 7.1 | Performance, thermal and electrical current evaluation of our controller at |     |

|     | 25 °C.                                                                      | 106 |

| 7.2 | Performance, thermal and electrical current evaluation of our controller at | ]   |

|     | <u>35 °C.</u>                                                               | 106 |

| 8.1 | The canonical phase composition of different workloads.                  | 115 |

|-----|--------------------------------------------------------------------------|-----|

| 8.2 | DVFS settings (MHz) of the phase-aware performance-energy trade-off      |     |

|     | table (PET).                                                             | 117 |

|     |                                                                          |     |

| 8.3 | CPU evaluation of the proposed technique using Geekbench4 (Higher scores |     |

|     | mean better performance).                                                | 121 |

|     |                                                                          |     |

| 8.4 | CPU-GPU evaluation of the proposed technique using 3DMark (Higher        |     |

|     | scores mean better performance).                                         | 100 |

## Chapter 1

### Introduction

### **1.1 Problem Characterization**

Mobile devices have become an indispensable tool of daily life, with 6.64 billion smartphone users across the globe. The evolution of mobile devices towards multi-purpose portable devices, used for communication, computing and entertainment is the main reason behind their widespread. Mobile usage is expected to keep growing in the future, as mobile technologies are becoming more affordable and available than ever. The increasing computing capabilities of mobile devices enabled them to replace desktop computers in many tasks, and with the advent of new technologies like Virtual and Augmented Reality, mobile devices are taking an even more important role.

The growth in the number of transistors per silicon die has been one of the main driving forces in the improvement of the computing capabilities of Mobile SoCs. Moore's law predicted that the number of transistors in a dense integrated circuit doubles about every two years. The slowing of Moore's law has led the industry to explore other directions, such as the design of heterogeneous multi-processor designs and the integration of specialized hardware units.

The combination of these different technologies enabled new applications and features that require intensive computation, raising critical thermal, power, and energy constraints:

• Thermal and power constraints: As technology scales down, power density considerably increases, raising critical power and thermal challenges. This is even more challenging for mobile devices due to their form factor, the multiple sources of thermal emergencies, their limited cooling capabilities, as well as the limited electric current delivery, arising from battery specifications. Elevated chip temperature triggers performance throttling mechanisms, making such temperature levels a major performance bottleneck [73, 58, 83]. Preventing thermal violations while sustaining the performance at acceptable levels led thermal management to become a critical factor in determining the user experience. The temperature limits are usually defined by the junction temperature of the chips, which has to be maintained usually under 90 °C. The other temperature that defines the limits for mobile devices is the skin temperature, which has to be maintained under 40 °C; otherwise, the mobile device would create a burning sensation to the end user [23, 29, 32, 41]. Additionally, the electric current should be sustained at safe levels to respect the battery discharge rate and the deterioration of the battery cells [85, 38, 45]. As mobile devices are battery-powered, there are hardware and software mechanisms that keep the current within the battery discharge specifications. In case the current exceeds some predefined value, the software mechanism throttles the frequency, with a fall back to the hardware mechanism, which shuts down the phone for safety reasons. Thus, it is essential to devise runtime management techniques that can prevent thermal and power violations, while maximizing the performance.

• Energy constraints: Battery lifetime has become one of the top usability concerns of mobile systems [81]. The phone form factors impose a strict limit to the battery size that can be accommodated. Thus, mobile devices are highly battery constrained because users are implicitly expected to charge their mobile devices once a day. On the other hand, the functionality integrated into such devices, and consequently their power consumption will continue to grow. Various studies [51], 40, 53] tried to build systems that adaptively balance performance and battery lifetime, since the user experience is mainly determined by these two factors. Thus developing energy management techniques to provide an extended battery lifetime, while meeting the user performance expectation is critical for the user experience.

#### **1.2 Major Thesis Contributions**

In this section, we outline the major contributions made in this thesis regarding the exploration of new techniques of thermal and power sensing and management for mobile system-on-a-chip.

1. Alternating Blind Identification of Power Sources for Mobile SoCs: In Chapter 3 we introduce Alternating Blind Identification of Power sources (Alternating-BPI), a technique that accurately estimates the power consumption of individual SoC units without the use of any design based models. The proposed technique uses a novel approach to blindly identify the sources of power consumption, by relying only on the measurements from the embedded thermal sensors and the total power consumption. The accuracy and applicability of the proposed technique was verified using simulation and experimental data. Alternating-BPI is able to estimate the power at the SoC hardware unit level with up to 98.1% accuracy. Furthermore, we demonstrate the applicability of the proposed technique on a commercial SoC and provide a fine-grain analysis of the power profiles of CPU and GPU Apps, as well as Artificial Intelligence (AI), Virtual Reality (VR) and Augmented Reality (AR) Apps. To summarize, the contributions of this chapter are as follows:

- We introduce the first Alternating Blind Identification of Power sources (Alternating-BPI). The new approach allows a better accuracy and practicality than previous blind identification techniques, and works on both simulation and experimental data, as it does not require steady thermal states.

- The proposed technique substantially decreases the power estimation error, especially for heterogeneous SoCs with multiple hardware units. Simulation data has shown that the proposed technique decreases the power estimation error as low as 1.9%, as compared to 11.2% for BPI [66]. Furthermore, we show that the accuracy of the proposed technique remains stable when moving from homogeneous to heterogeneous architectures, and remains stable when the number of hardware units increase. As opposed to BPI [66] and BPISS [72], whose accuracy dropped when increasing the number of units and moving to heterogeneous architectures.

- The technique is used to design a plug and play tool, that is made publicly available [16], and that allows to estimate the power consumption of SoC units.

- The proposed technique is demonstrated using simulated and experimental data. Then it is used to characterize the power profile of several benchmarking Apps on a commercial SoC, including : CPU, GPU, Artificial Intelligence (AI) , Virtual Reality (VR), Augmented Reality (AR) Apps. The power characterization provides insights about the power efficiency of the different hardware units on a state-of-the-art commercial SoC.

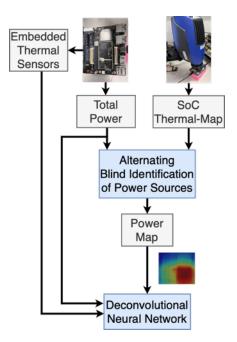

- 2. Deconvolutional Neural Network Based Power Map Estimation: In chapter 4, we propose an approach for full-chip power map estimation based on Deconvolutional Neural Networks (DCNN). The proposed approach relies on the usage of the few available embedded thermal sensors on the SoC to estimate the full SoC power map. The contributions of this chapter are as follows:

- We propose to solve the power map estimation problem as an image generation problem using Deconvolutional Neural Networks (DCNN). The proposed DCNN takes as input the thermal measurements from the embedded thermal sensors and the total power to estimate the full SoC power map.

- The proposed technique allows to estimate the power map at a finer spatial granularity than the thermal spatial granularity of the existing thermal sensors. More specifically, it allows to estimate the power even at locations where thermal measurements are not physically available.

- The proposed technique is demonstrated using a commercial SoC while running several benchmarks. The predicted power maps show a 97% similarity (2D correlation) with the power maps estimated using the Alternating-BPI.

- 3. Power and Hardware Characterization of Augmented Reality Applications: In Chapter 5, we take a step towards the improvement of the Augmented Reality mobile experience by performing a power and hardware characterization of Augmented Reality Applications. The characterization includes designing and developing AR-Bench, an augmented reality benchmark for mobile devices. We provide an analysis of the existing AR Apps in terms of performance, power and hardware utilization to motivate the design of ARBench. The proposed benchmark includes various workloads, such that each workload evaluates a particular aspect of AR workloads by stressing multiple hardware units of the SoC (CPU, GPU, DSP, etc). Then, AR-Bench is used to evaluate the AR performance of existing commercial mobile de-

vices and Android operating systems. Furthermore, we use ARBench to perform a phase analysis to identify a set of canonical phases that could be used to model AR workloads, and use them to characterize existing AR Apps. Finally, the benchmark is used to study the performance and power trade-offs of different CPU multicore configurations, and we provide insights that could be used to save power while meeting the AR performance requirements. To summarize, the contributions of this chapter are as follows:

- We characterize the hardware utilization of several AR Apps using a commercial device. Then, we analyze the power consumption per-hardware unit and per-AR process.

- While existing AR benchmarks mainly target Desktop computers, we design and develop ARBench, the first AR benchmark that measures the AR performance of mobile devices. The benchmark incorporates different AR workloads that stress multiple hardware units of the SoC (e.g. CPU, GPU, DSP), and measures the individual score for each AR workload.

- We provide insights about the ability of existing mobile devices to run AR workloads, by using ARBench to evaluate the performance of several commercial mobile devices and Android Operating Systems. The performance results are shown for each individual AR workload.

- We use ARBench to perform a phase analysis to identify a set of canonical phases that could be used to model and characterize AR workloads.

- We study the performance and power trade-off of different multi-core CPU configurations, and provide insights about the most efficient multi-core configuration that could run the AR workloads, while meeting the performance requirements.

- 4. Coordinated Self-tuning Thermal Management Controller for Mobile Devices: In Chapter 6 we propose a coordinated self-tuning thermal management controller on the basis of online deep learning that continuously adapts to characteristics and operating conditions. Furthermore, our controller takes into account both skin temperature and junction temperature constraints in a coordinated manner. To summarize, the contributions of this chapter are as follows:

- We design a junction temperature controller that continuously tunes the proportional-integral-derivative (PID) parameters on the basis of online learning. The controller uses a neural network (NN) that updates its weights according to the operating conditions to reduce thermal violations while maximizing performance.

- We design an NN-based coordinated self-tuning thermal management controller that manages both the skin and the junction temperature by proactively scaling the junction temperature threshold.

- We implemented a low-overhead controller on a real smartphone and we evaluate it comprehensively compared to PID [84], thermal-aware DVFS controller [48] and USTA [41], under different ambient temperatures and workload characteristics. Our results demonstrate that our coordinated self-tuning thermal controller leads to 6% better performance, and spends up to 27× less time in thermal violation.

- 5. CasCon: Cascaded Thermal And Electrical Current Throttling for Mobile Devices: In Chapter 7, we propose a cascaded thermal and electrical current throttling controller inspired from the physical relations that exist among the different current and thermal measures. The proposed controller achieves better results by coordinating between the different sources of current and thermal emergencies, and dynamically adjusting their caps. Testing on a state-of-the-art smartphone, the proposed technique achieves 6.5% better performance and 18% power savings as compared to existing techniques, while avoiding current and thermal violations using 40× less DVFS transitions. To summarize, the contributions of this chapter are as follows:

- We design a cascaded controller (CasCon) that manages the skin temperature, the junction temperature and the electrical current in a coordinated manner. In contrast to existing work, where the skin and junction temperature, and the electrical current are managed separately, leading to a sub-optimal control.

- In contrast to existing work, the proposed controller dynamically changes the thermal and electrical current caps in runtime, allowing it to save power and improve performance. We also introduce a frequency locking function that significantly reduces the number of DVFS transitions, hence bringing extra power savings.

- We implement our CasCon controller on a real smartphone and we evaluate it comprehensively at different ambient temperatures. Our results show that the proposed controller successfully prevents current and thermal violations even at high ambient temperatures, while bringing up to 6.5% performance improvements and 18% power savings compared to previous work.

- 6. Workload- and User-aware Battery Lifetime Management for Mobile SoCs: In Chapter 8 we propose a CPU-GPU workload- and user- aware battery lifetime management technique for mobile devices using machine learning. Firstly, we design a workload-aware governor through an offline and an online analysis. A set of CPU and GPU performance counters is used during the offline analysis to identify a set of canonical phases (CP). In runtime, k-means is used to classify each sample of the performance counters to one of the predefined CP. Afterwards, we build a model that predicts the energy consumption given the user usage history. Finally, the energy model is used to find the optimal frequency settings for the CPU and GPU to provide the best performance while meeting the target battery lifetime. The evaluation of the proposed work against state of the art techniques in a commercial smartphone, shows 15.8% and 9.4% performance improvement on the CPU and GPU, respectively. The proposed technique also shows 10× improvement in performance variation, while meeting the desired battery lifetime. To summarize, the contributions of this chapter are as follows:

- We design the first workload- and user-aware battery lifetime management technique. The workload-awareness is achieved through performance counters, while the user awareness is incorporated by representing the user-usage history through a set of canonical phases (CP).

- We propose a novel model that predicts the energy consumption based on the user usage history. This model makes the proposed technique user-aware, and helps in better meeting the user desired lifetime.

- The proposed battery lifetime management is achieved by scaling both the CPU and the GPU DVFS levels, unlike previous techniques that do not consider the GPU.

- We implement our technique on a commercial smartphone and compare its

performance against state-of-the-art battery management techniques. We show that our technique achieves 15.8% and 9.4% performance improvement on the CPU and GPU, respectively, while meeting the lifetime target and decreasing the performance variation by 10x.

The organization for the remainder of this thesis is as follows. Chapter 2 briefly describes the background and related prior work. Next, Chapter 3 presents our proposed Alternating Blind Identification of Power source technique. Chapter 4 introduces the Deconvolutional Neural Networks based power map estimation. Chapter 5 shows the results of the power and hardware characterization of Augmented Reality Applications. Next, we introduce our proposed coordinated self-tuning thermal management controller in Chapter 6 In Chapter 7, we propose CasCon, a cascaded thermal and electrical current throttling controller for mobile devices. Chapter 8 introduces a novel workload- and useraware battery lifetime management technique. Finally, Chapter 9 summarizes the results and findings of this thesis and provides possible future extensions of this work.

### Chapter 2

### Background

In this chapter, we describe the background and related prior work to the proposed techniques in this dissertation. We start by introducing thermal and power sensing background for Mobile SoCs in Section 2.1] In Section 2.2, we introduce related work to thermal and power runtime management. Finally, in Section 2.3 we introduce related work to energy and battery lifetime management.

### 2.1 Thermal and power sensing

The ability to measure power consumption of different hardware units is essential for the operation and improvement of mobile SoCs, as well as the enhancement of the power efficiency of the software that runs on them. Mobile SoCs are usually enabled with embedded thermal sensors to measure the temperature at the hardware unit level; however, they lack the ability to sense the power. Thus, devising techniques that enable fine-grain level power profiling of Mobile SoCs, and the software that runs on them, is a major step towards im-

plementing efficient power and thermal management techniques, as well as, designing the architecture of the next generation Mobile SoCs.

Various studies investigated a wide range of methods for thermal and power modeling of heterogenuous SoCs. The standard approach used by these techniques try to identify the state space model that links temperature to power [66, 72, 25, 35, 78] :

$$\mathbf{t}(k) = \mathbf{A}\mathbf{t}(k-1) + \mathbf{B}\mathbf{p}(k), \qquad (2.1)$$

where t(k) an p(k) are vectors that denote the temperature and power of the SoC hardware units at time k, respectively. Both A and B are two modeling matrices that capture the physical relationship between power and temperature. More precisely, the A matrix represents the thermal conductance matrix, which describes the natural response of the system, in the absence of power. The B matrix represents the forced response matrix, and it is function of the thermal capacitance and the thermal conductance matrices. Both the A and B are square matrices, whose dimension is equal to the number of power sources. The state space model in Equation [2.1] is derived from the heat diffusion equation [56], which describes the power-thermal interaction by taking into consideration the thermal conductivity, the density and the specific heat of the material. More specifically, the derivation of the model in Equation [2.1] is performed by applying a spatial discretization on the heat diffusion equation [56] , followed by a temporal discretization.

Being able to compute the state space modeling matrices would make it possible to estimate and predict the power consumption, at the same level of granularity as the available thermal measurements. In the case where thermal measurements are unavailable, and power measurements are available, being able to compute the modeling matrices would make it possible to predict the temperature, at the same level of granularity as the available power measurements. There are three general approaches to identify the state space model:

- 1. Design based approach: it is usually based on pre-silicon data and requires access to the design proprietary information, such as its layout and gate level netlist, its materials and heat sink configuration [47, 28, 57]. Thus, this approach assumes the availability of A and B and attempts to estimate p(k). Skadron *et al.* [77] designed an approach that models thermal behavior of the die and its package as a circuit of thermal resistances and capacitances, that correspond to functional blocks at the architecture level, which helps in capturing the physical relationship that relates power to temperature, which is similar to finding the A and B matrices. However, this is not a practical solution, since it is design specific, and it is prone to errors related to variability in the semiconductor manufacturing process. Additionally, it is computationally challenging to conduct large-scale gate-level simulation.

- 2. Runtime based approach: it considers the processor as a gray box, and it identifies the state-space models based on physical measurements. Most of these techniques use system identification techniques and mainly rely on the existence of sensors for the power sources [25, 52, 27]. Thus, this approach assumes the availability of p(k) and attempts to estimate A and B. However, such fine-grain power sensors are unavailable on mobile SoCs. Another type of runtime approach, relies on the usage of infrared imaging and performance counter measurements [68, 39], however, performing infrared imaging might be invasive and prone to noisy measurements. Other runtime based techniques focus on the usage of performance counters to model the power, for instance, Min *et al.* [54] proposed a general approach to build system power estimation models based on hardware performance counters. Karan *et al.* [75] derive functions for real time estimation of system power consumption using performance counters. Kim *et al.* [49] proposed a statistical approach for build-

ing power models using performance counters as effective proxies for x86 systems. However, all the previous techniques assume the existence of power sensors and do not perform their power modeling at the fine-grain level.

3. The blind identification approach: it makes no assumption about the availability of modeling matrices and the fine-grain power sensors. This approach relies on the total power and the fine-grain thermal sensors to estimate both the modeling matrices and the power sources [66]. This technique relies on the steady state thermal data to estimate the B matrix. However, usually in practice it is not possible to reach steady thermal state on modern SoCs. This affects the accuracy of the model and makes it less convenient to use in practice.

The challenging task of getting fine-grain power measurements has led to the existence of only few studies that provide useful insights about the power consumption and efficiency of the different SoC hardware units while stressed by various software applications [59, 30, 72].

#### 2.2 Thermal and power runtime management

Mobile devices are battery-powered and composed of various computing units with a very constrained form factor. More specifically, mobile devices should stay small enough to hold and operate in the hand. As a result, only limited cooling techniques can be used. The increasing user demand and the emerging new technologies are pushing the power density of System-on-chips (SoCs) to new boundaries. This increase leads to more power and thermal challenges, which have been investigated in various studies:

• Junction temperature management: Form-factor constraints make thermal management on mobile devices a unique challenge as compared to thermal management on desktop or server processors. For instance, mobile SoCs have much faster thermal transient than desktop processors since the thermal capacitance of their cooling systems is significantly lower. Elevated chip temperature triggers performance throttling mechanisms, making such temperature levels a major performance bottleneck. Thermal modeling and predictive models have been widely investigated. In particular, Gaurav *et al.* [76] used a power and thermal model to predict temperature to dynamically compute a power budget based on which the frequency is determined. Prakash et al. [64] proposed CPU-GPU coordinated thermal management using two separated PID controllers and thermal prediction. A RC model that reflects the thermal coupling between the battery and the application processor is proposed by Xie *et al.* [79]; the model is then used to predict the temperature and pre-compute safe frequencies online. Achieving sustainable performance by compromising short term performance was investigated by Sahin *et al.* in [70] and [71], where a quality-aware frequency scaling is proposed to improve performance sustainability. Different tracks in thermal management were also investigated. Bartolini et al. [26] designed energy aware thermal controller, based on prediction models. Kim et al. in [48] proposed a thermal-aware DVFS scaling scheme for mobile devices that stabilizes the frequency by averaging over a moving window. Cochran et al. [36] proposed thermal prediction and adaptive control phase detection based on performance counters. Even if various elaborated techniques have been proposed in the literature, in commercial smartphone the most conventionally used thermal management controller is the PID, whose overall control function can be expressed mathematically as:

$$u(t) = K_p e(t) + K_i \int_0^t e(t') dt' + K_d \frac{de(t)}{dt},$$

(2.2)

where  $K_p$  is the proportional gain,  $K_i$  is the integral coefficient and  $K_d$  is the derivative coefficient, while u(t) and e(t) represent the control signal and the error between the current maximum temperature and the thermal threshold of the CPU, respectively. The tuning of the PID parameters determines the performance of the controller. The mostly used tuning method is Zigler-Nichols [84].

Zigler-Nichols [84] is a heuristic method based on a closed-loop system, where the  $K_i$  and  $K_d$  gains are first set to zero. The  $K_p$  gain is then increased (from zero) until it reaches the critical gain  $K_{cr}$ , at which the output of the control loop has sustained oscillations with period  $P_{cr}$ . Finally,  $K_{cr}$  and the oscillation period  $P_{cr}$  are used to set the  $K_p$ ,  $K_i$ , and  $K_d$  gains, where  $K_p = 0.6K_{cr}$  and  $T_i = 0.5P_{cr}$ , and  $T_d = 0.125P_{cr}$ . Once the oscillatory settings are dialed back according to the Zigler-Nichols coefficients (i.e., 0.6, 0.5, and 0.125), the controller no longer leads to a sustained thermal oscillation state, but rather a stable thermal behaviour.

• Skin temperature control: Another challenge about mobile devices is that they are handheld; thus, the whole device's temperature has to be limited because of skin temperature [44]; otherwise, it would adversely impact the user's experience. It has been shown that the skin temperature could be a performance limiter [79, 55, 60, 41]. The authors [79] showed that the performance is linearly related to the skin temperature. Park *et al.* [60] conducted experiments to explain the relationship between the operating characteristics and heat generation for all active components in a smartphone device, then they developed a thermal prediction model that accurately predicts the skin temperature of a mobile device. Skin temperature management has not been as widely investigated as the junction temperature management, however a User–specific skin temperature-aware (USTA) is proposed in [41]. The technique relies on a machine learning model to predict the skin temperature, which is derived offline based on empirical data gathered from thermal measurements.

• **Current throttling:** As mobile devices are battery-powered, the electric current should be sustained at safe levels to respect the battery discharge rate and the deterioration of the battery cells [82]. There are hardware and software mechanisms that keep the current within the battery discharge specifications. In case the current exceeds some predefined value, the software mechanism throttles the frequency, with a fall back to the hardware mechanism, which shuts down the phone for safety reasons.

### **2.3** Energy and battery lifetime management

Battery lifetime has become one of the top usability concerns of mobile systems [81]. The user experience, for battery powered-devices, depends on both performance and battery lifetime.

Various studies tried to offer better energy savings by studying DVFS governors. In particular, a hierarchical FSM-based frequency capping technique was proposed to save power by allowing minor degradation in performance [61]. Choi *et al.* designed a graphics-aware power governing technique that solves the energy inefficiency of frame rendering [33]. A memory-aware cooperative CPU-GPU DVFS governor was proposed to maximize the energy efficiency while meeting a performance target [46]. A phase-aware web browser power management technique was proposed by Peters *et al.* [62]. In an other study, an energy-efficient mobile web interaction framework that leverages a cloud-based machine learning model was proposed [80]. Most of these techniques allow a slight degradation in performance to improve the energy efficiency, as result, they do not properly offer a fine-grain balancing of the performance and the battery lifetime. Furthermore, they do not take into consideration the user's desired battery lifetime goal.

The most used technique in commercial smartphones for battery lifetime management is Powersave [42]. It sets the allowed frequency to the highest possible level, and when 20% of the battery capacity is reached, the allowed frequency is set to a lower level.

Prior studies have also explored improving the user satisfaction by balancing the battery lifetime and the performance. Yan *et al.* [81] proposed a quality of experience (QoE)aware frequency governor which dynamically scales the CPU frequency at low battery levels. Donohoo *et al.* [40] proposed a framework that optimizes the CPU and the screen backlight energy consumption. Poyraz *et al.* [63] used built-in sensors to predict the user satisfaction for CPU Settings to save energy. In a recent study, Lee *et al.* [51] proposed BUSQ1 and BUSQ3, two dynamic quality of service (QoS) scaling approaches that automatically balance QoS and energy. BUSQ1 defines the discharge profile linearly, while BUSQ3 defines it based on the user usage history. Afterwards, by comparing the current battery status against the predefined discharge profile, the frequency is decreased if energy savings are needed and is increased otherwise. However, the previously mentioned studies do not take into consideration the GPU. Furthermore, most of these studies do not leverage any workload-awareness, rather, they scale the frequency independently of the running workload. Thus, wasting several opportunities to save energy or to improve performance.

### Chapter 3

# Alternating Blind Identification of Power Sources for Mobile SoCs

In this chapter, we investigate the use of a new approach that relies on an Alternating-BPI algorithm to blindly estimate the power at the SoC unit level. We use the proposed technique to develop a plug and play tool that allows to identify the power consumption of the different SoC units. Using the proposed technique, we provide a fine-grain power analysis of a commercial SoC and provide useful insights about its power efficiency. The contributions of this chapter are as follows:

- We introduce the first Alternating Blind Identification of Power sources (Alternating-BPI). The new approach allows a better accuracy and practicality than previous blind identification techniques, and works on both simulation and experimental data, as it does not require steady thermal states.

- The proposed technique substantially decreases the power estimation error, especially for heterogeneous SoCs with multiple hardware units. Simulation data has

shown that the proposed technique decreases the power estimation error as low as 1.9%, as compared to 11.2% for BPI [66]. Furthermore, we show that the accuracy of the proposed technique remains stable when moving from homogeneous to heterogeneous architectures, and remains stable when the number of hardware units increase. As opposed to BPI [66] and BPISS [72], whose accuracy dropped when increasing the number of units and moving to heterogeneous architectures.

• The proposed technique is demonstrated using simulated and experimental data. Then it is used to characterize the power profile of several benchmarking Apps on a commercial SoC, including : CPU, GPU, Artificial Intelligence (AI), Virtual Reality (VR), Augmented Reality (AR) Apps. The power characterization provides insights about the the power efficiency of the different hardware units on a state-of-the-art commercial SoC. Some of the insights include: (1) Even with the new integrated computing units to modern Mobile SoCs, like the GPU, the image signal processor and neural engine, the CPU is still the main source of power consumption, representing around 60% to 75% of the total SoC power. (2) The little CPU cluster plays a major role in saving power, with a power consumption that is 5x less than the big CPU cluster. (3) The GPU power consumption for AR Apps, represents only 9% of the total SoC power consumption, while the CPU represents 75% of the total SoC power consumption.

The rest of the chapter is organized as follows: Section 3.1 motivates the proposed work. Section 3.2 describes the proposed technique and the underlying physical and mathematical concepts, and it introduces the Alternating-BPI tool. Section 3.3 presents the evaluation results of our technique compared against state-of-the-art techniques, as well as the power characterization of different benchmarking Apps on a commercial SoC. Section 3.4 concludes the chapter.

# 3.1 Motivation

The higher power density and limited cooling solutions for mobile SoCs is pushing mobile devices towards a major performance bottleneck [44]. Thus, devising techniques and tools that help in profiling at a fine-grain level the existing SoCs, and the software that runs on SoCs, is a major step towards implementing efficient power and thermal management techniques, as well as, designing the architecture of the next generation Mobile SoCs.

Sensing the power and temperatures of the different hardware units in modern SoCs is a key enabling efficient and optimal power and thermal management techniques. Additionally, a fine-grain map of the power consumption of modern SoCs across different software applications would provide valuable insights to improve the performance of SoCs at the hardware and software level. However, modern processors provide only coarse-grain power measurements of all cores using the running average power limit (RAPL) [37]. Various techniques from the literature rely on different assumptions and offer different levels of accuracy, practicality, and feasibility have been proposed [28, 57, 27, 39].

The availability of thermal sensors on a per-hardware unit basis on mobile SoCs, makes it possible to estimate the power consumption at the unit level using blind identification techniques. Blind Power Identification (BPI) [66, 67, 72] was proposed to estimate the power at the SoC unit level, based on the individual thermal measurements and the total power consumption. However, BPI [66] relies on the thermal steady state data to estimate the power model parameters, which is hard to generate in practice and might affect the accuracy. The reliance on certain tools and assumptions, the insufficient accuracy and the lack of practicality of the available power identification techniques has led to the lack of techniques that provide a fine-grain power measurements of modern SoCs.

### **3.2** Alternating Blind Identification of Power sources

### **3.2.1** The proposed approach

The proposed approach consists of identifying the state space modelling matrices with a better accuracy. The state space model given by:

$$\mathbf{t}(k) = \mathbf{A}\mathbf{t}(k-1) + \mathbf{B}\mathbf{p}(k), \qquad (3.1)$$

where t(k) an p(k) are vectors that denote the temperature and power of the SoC hardware units at time k, respectively. Both A and B are two modeling matrices that capture the physical relationship between power and temperature. More precisely, the A matrix represents the thermal conductance matrix, which describes the natural response of the system, in the absence of power. The B matrix represents the forced response matrix, and it is function of the thermal capacitance and the thermal conductance matrices. Both the A and B are square matrices, whose dimension is equal to the number of power sources.

The proposed technique consists of two steps: *Off-line Training* step and *Runtime Estimation* step. The *Off-line Training* step needs to be run only once for each SoC, to capture the modeling matrices. The *Runtime Estimation* needs to be run each time the per-SoC unit power needs to be identified, its little computation overhead allows it to run on the device in runtime.

In the *Off-line Training* step a training data is required as input. It consists of the per-unit SoC thermal measurements and the total power consumption. The thermal measurements are generated while stressing the SoC hardware units using different patterns

separated by sleep periods. More precisely, different combination of stressed and idle units should be part of the training data. This allows to capture thermal transients, and the contribution of the different units to the total power. The output of the *Off-line Training* is the state space model matrices **A** and **B**. On Algorithm 1, the *Off-line Training* step is shown through lines 1 to 5, which shows how the **A** and **B** matrices of Equation 3.1 are identified.

First, the natural response matrix is estimated using the transient temperature traces. After stressing the cores with a workload, the power is forced to p(k)=0. In practice, this could be achieved by stopping the running workload, and turning-off the target hardware units. Thus from Equation [3.1], we get:

$$\mathbf{t}(k) = \mathbf{A}\mathbf{t}(k-1),\tag{3.2}$$

Equation 3.2 is used to determine the A matrix through least square minimization, as shown in line 1 of Algorithm 1. This minimization is solved under the positivity constraint of the A matrix, since the A matrix represents the thermal conductance matrix, as explained earlier in Chapter 2.

Next, the goal is to make an initial guess about the B matrix. During a steady temperature state, there is no thermal variation, so the temperature at time k would be equal to temperature at time k - 1, i.e.  $\mathbf{t}(k) \approx \mathbf{t}(k - 1) = \mathbf{t}_s$ , which gives the following using Equation 3.1:

$$\mathbf{t}_s \approx \mathbf{A} \mathbf{t}_s + \mathbf{B} \mathbf{p}_s, \tag{3.3}$$

Algorithm 1: Alternating Blind Identification of Power Sources.

**Input:** Temperatures t(k), Total power of p(k)

**Output:** Natural Response Matrix **A**, Forced Response Matrix **B**, Power Profiles **p**(k)

1 Find the Natural Response Matrix A through the least square minimization:

$$\min |\mathbf{t}(k) - \mathbf{At}(k-1)|^2$$

under the constraint  $\mathbf{A} \succeq 0$

2 Initialize the B matrix :

$$\mathbf{R} = (\mathbf{J} + \mathbf{I})/3$$

$$\mathbf{B} = (\mathbf{I} - \mathbf{A})\mathbf{R}$$

where I is the identity matrix, J is an all ones matrix, and R is the thermal transfer matrix

- **3 Repeat Power and B-Matrix estimation steps for n times:**

- **4 P**-*step*: Using quadratic programming find  $\mathbf{p}(\mathbf{k}) \succeq 0$  such that:

$$\min \mathbf{Bp}(k) - (\mathbf{t}(k) - \mathbf{At}(k-1))_2$$

$$\mathbf{p}(k)_1 = \mathbf{p_{tot}}(\mathbf{k})$$

where  $\mathbf{p_{tot}}(\mathbf{k})$  is the measured total power at time k

5 B-*step*: Using least square minimization find B given p(k) and A :

$$\min |\mathbf{Bp}(k) - (\mathbf{t}(k) - \mathbf{At}(k-1))|^2$$

**6 Runtime estimation:** Given the **A** and **B**, and the target thermal and total power data, solve the quadratic programming of the **P** step.

$$\mathbf{t}_s \approx (\mathbf{I} - \mathbf{A})^{-1} \mathbf{B} \mathbf{p}_s, \tag{3.4}$$

$$t_s \approx Rp_s,$$

(3.5)

where  $t_s$  and  $p_s$  represent the temperature and the power at the steady-state, and the R matrix represents the *steady-state thermal transfer matrix*. The previous equations help in defining the thermal transfer matrix R as:

$$\mathbf{R} = (\mathbf{I} - \mathbf{A})^{-1} \mathbf{B}, \tag{3.6}$$

based on the physical relationship between power and temperature on a multi-unit configuration, the  $\mathbf{R}$  matrix should be a symmetric matrix with maximum values on the diagonal. Thus, the initialization shown in line 2 of Algorithm []. The initial guess about the  $\mathbf{R}$ matrix is then used to initialize the  $\mathbf{B}$  matrix using:

$$\mathbf{B} = (\mathbf{I} - \mathbf{A})\mathbf{R},\tag{3.7}$$

after initializing the B matrix, in line 3 to 5 of Algorithm  $\boxed{1}$  we determine the B matrix by alternating *n* times between two steps, *n* being a hyperparameter:

- P-step: estimates p(k), the power consumption per-SoC unit, given an initial guess of the B matrix. This is achieved by solving the quadratic programming optimization shown in line 4 of Algorithm []. The optimization is solved under two constraints. The first constraint is the positivity constraint of p(k), since it represents power values. The second constraint ensures that the sum of the power consumption of the SoC units at time k, is equal to ptot(k), the measured total power at time k. The number of unknowns in this step is equal to the number of the target SoC units times the number of timestamps.

- B-*step*: estimates the B matrix using least squares minimization, as shown in line 5 of Algorithm [], given p(k) from the P-*step* and the A matrix from line 1 of

Algorithm []. The number of unknowns in this step is equal to number of elements of the B matrix, which is the square of the number of SoC units, for which the power is identified.

Simulation and experiment data has shown that a higher number of iterations n brings a better accuracy, however, 10 iterations could be sufficient in most cases.

After identifying the modeling matrices A and B, in the *Runtime Estimation* step any thermal and power data can be given as input to estimate the power per-SoC unit. The *Runtime Estimation* step estimates the power per-SoC unit by solving the same quadratic programming as in the P-*step*. The user will have to only provide the temperature values per-SoC unit and the total power consumption, this data will be used along with the A and B matrices determined in the off-line training step, to determine the power consumption per-SoC unit.

#### **3.2.2** The Alternating-BPI tool

The goal of the Alternating-BPI tool is to make the fine-grain power analysis under various devices seamless and straightforward. This would enable the research community with a tool that helps in providing useful insights, in order to improve modern SoCs. The Alternating-BPI tool [16], shown in Figure 3.1, puts under the same package Algorithm 1 and the necessary data processing techniques to automate the whole process of the blind power identification.

As shown in Figure 3.1, the tool is composed of an *Off-line Training* step and *Runtime Estimation* step. During the *Off-line Training* the tool processes the data and estimates the A and B matrices. Then, during the *Runtime Estimation*, it estimates the power per

Figure 3.1: The Alternating-BPI tool.

SoC unit of any given data. The composing elements of the tool shown in Figure 3.1 are explained below:

- The training data: is a matrix that includes the total power consumption of the SoC on the first column, and the temperature per-SoC unit on the remaining columns. The training data should be generated by stressing the different SoC units in different patterns, separated by idle states, where a pattern is identified as a combination of active and idle SoC units. The best results are obtained when the data is collected for all the possible patterns, which requires going through all the possible configurations of active and idle SoC units. Collecting the thermal data for different patterns helps in estimating the contribution of each SoC unit to the total power, while the idle states help in creating transient thermal state data, that is used to estimate the **A** matrix.

- The target data: this data does not have to follow any specific patterns as required for the training data. The target data represents the data points for which the user wants to identify the power consumption per-SoC unit. It consists of the total power consumption and the temperature per-SoC unit.

- Thermal transients identification: the goal of this step is to identify the thermal transients on the training data. The thermal transients correspond to the natural response temperature variations that are described by Equation [3.2]. The thermal

transients are identified by tracking the thermal variation over a sliding window, if the thermal variation exceeds a certain predefined threshold, it is considered as a thermal transient. When a thermal transient is detected, the thermal data points within a predefined range are considered as part of the thermal transient trace and are saved in a matrix. This process is applied to all the training data until all the transient states are detected and recorded. The output of this step, is the thermal transient states.

- A Matrix identification: This step uses the thermal transients identified in the previous step to identify the A matrix, as shown on line 1 of Algorithm 1.

- B Matrix identification: This step estimates iteratively the B Matrix using the training data given as input, by alternating between the estimation of the B matrix and p(k), as shown on line 2 to 5 of Algorithm 1.

- Identification of the power sources: This step is about the identification of the power consumption per-SoC unit of the target data, given the A and B matrices. This corresponds to the runtime estimation step explained in Algorithm 1. This step is fast enough to generate the power values in real-time, for instance, using an Intel I5-7360U CPU processor, it takes as low as 1.5 ms to generate the power data of 8 SoC units for one timestamp. This makes the proposed technique fast enough to be deployed to generate power predictions in real-time.

Figure 3.2: The verification and testing flow of the Alternating-BPI.

## **3.3 Experiments and Results**

### 3.3.1 Experimental setup

**Simulation setup:** The accuracy of the proposed technique is verified using the HotSpot thermal simulator [47]. As shown on Figure 3.2, for a given design layout, the HotSpot thermal simulator [47] takes as input the per-unit power traces, and produces the corresponding per-unit temperature traces. Figure 3.2 shows that the per-unit temperature traces, from the HotSpot simulator [47], are then taken as input by the proposed Alternating-BPI tool along with the total power. The estimated per-unit power, by the Alternating-BPI tool, is then computed. Finally, the accuracy of Alternating-BPI is computed by comparing the difference between the per-unit power traces given to HotSpot [47] as input, and the estimated per-unit power by the Alternating-BPI.

We follow the same methodology as in [67], and we choose three different floorplan benchmarks:

• 2x2 mesh : a floorplan composed of 4 units with a total maximum power budget of 80 W, and 1 cm x 1 cm as the floorplan dimensions.

|               |  | big<br>core 1 | big<br>core 0 |

|---------------|--|---------------|---------------|

|               |  |               |               |

| LITTLE<br>CPU |  | big<br>core 3 | big<br>core 2 |

|               |  | GPU           |               |

Figure 3.3: Layout of the big.LITTLE+GPU SoC [43] used for the testing of the Alternating-BPI.

- 3x3 mesh : a floorplan composed of 3 units with a total maximum power budget of 80 W, and 1 cm x 1 cm as the floorplan dimensions. This floorplan was chosen to test how the increase in the number of units could affect the per-unit power accuracy.

- big.LITTLE+GPU : as shown on Figure 3.3, this floorplan is composed of 6 units, with a total maximum power budget of 15 W, and 1 cm x 1 cm as the floorplan dimensions. This floorplan was chosen to test how the heterogeneity of the architecture could affect the per-unit power accuracy. Additionally, this floorplan benchmark reflects better the existing SoCs, which are mainly based on heterogeneous architectures.

**Development board setup:** There is no way to verify the accuracy of the per-unit power estimation on a real device, due to the lack of per-unit power sensors. Actually, the true motivation behind the proposed Alternating-BPI technique is to provide perunit power estimations, based on the per-unit temperature measurements, due to the nonexistence of per-unit power sensors. Despite this, a validation test could still be performed on a real device, by running different workloads and contrasting the per-unit power numbers based on the hardware specification of each unit, which could validate the results. For instance, the power consumption of the GPU should be significantly higher when running a GPU benchmark, as compared to running a CPU Benchmark. Additionally, we know from the hardware specification that certain CPU cores are designed for power efficiency, while other cores are designed to provide maximum performance, based on this we would expect the power numbers of the power efficient cores to be significantly lower, after taking into consideration the hardware utilization numbers. However, the exact accuracy of the proposed technique would still be verified based on the simulation data.