### Hardware-Software Co-design of Resource-Efficient Deep Neural Networks

by Hokchhay Tann

M.Sc., Brown University, Providence, RI, 2016 B.Sc., Trinity College, Hartford, CT, 2014

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in School of Engineering at Brown University

PROVIDENCE, RHODE ISLAND

May 2019

© Copyright 2019 by Hokchhay Tann

This dissertation by Hokchhay Tann is accepted in its present form by School of Engineering as satisfying the dissertation requirement for the degree of Doctor of Philosophy.

| Recommended to the Graduate Council | Recommended | to | the | Graduate | Council |  |

|-------------------------------------|-------------|----|-----|----------|---------|--|

|-------------------------------------|-------------|----|-----|----------|---------|--|

Date\_\_\_\_\_

Sherief Reda, Advisor

Date\_\_\_\_\_

Jacob Rosenstein, Reader

Date

Rodrigo Fonseca, Reader

Approved by the Graduate Council

Date\_\_\_\_\_

Andrew G. Campbell, Dean of the Graduate School

#### Vitae

Hokchhay Tann was born and raised in Pursat Province, Cambodia. He received his B.Sc. with double majors in Engineering (EE Concentration) and Mathematics from Trinity College, Hartford, CT in 2014. He received his M.Sc. in Electrical and Computer Engineering from Brown University in 2016 during his studies in the Ph.D. program. His main areas of research include approximate computing, resource-efficient design and accelerations of neural networks with applications to iris recognition and chemical computation.

hokchhay\_tann@brown.edu https://www.htann.com Brown University, RI, USA

#### **Selected Publications:**

- H. Tann, H. Zhao, S. Reda, "Resource-Efficient Embedded Iris Recognition Systems Using Fully Convolutional Neural Networks," under revision in ACM Journal of Emerging Technologies in Computing Systems (JETC), 2019.

- K. Nepal, S. Hashemi, H. Tann, R. I. Bahar and S. Reda, "Automated High-Level Generation of Low-Power Approximate Computing Circuits," in IEEE Transactions on Emerging Topics in Computing, vol. 7, no. 1, pp. 18-30, 1 Jan.-March 2019.

- 3. C. Arcadia, H. Tann, A. Dombroski, K. Ferguson, S. L. Chen, E. Kim, B. Ruben-

stein, C. Rose, S. Reda and J. Rosenstein, "Parallelized Linear Classification with Volumetric Chemical Perceptrons," in IEEE International Conference on Rebooting Computing (ICRC), 2018, pp. 1-9.

- S. Hashemi, H. Tann, and S. Reda, "BLASYS: Approximate Logic Synthesis Using Boolean Matrix Factorization," in ACM/ESDA/IEEE Design Automation Conference (DAC), 2018, pp. 1-6.

- S. Hashemi, H. Tann, F. Buttafuoco and S. Reda, "Approximate Computing for Biometric Security Systems: A Case Study on Iris Scanning," in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2018, pp. 319-324.

- H. Tann, S. Hashemi, R. I. Bahar and S. Reda, "Hardware-software codesign of accurate, multiplier-free Deep Neural Networks," in ACM/EDAC/IEEE Design Automation Conference (DAC), Austin, TX, 2017, pp. 1-6.

- S. Hashemi, N. Anthony, H. Tann, R. I. Bahar and S. Reda, "Understanding the impact of precision quantization on the accuracy and energy of neural networks," in Design, Automation & Test in Europe Conference & Exhibition (DATE), Lausanne, 2017, pp. 1474-1479.

- H. Tann, S. Hashemi, R. I. Bahar and S. Reda, "Runtime configurable deep neural networks for energy-accuracy trade-off," in International Conference on Hard-ware/Software Co-design and System Synthesis (CODES+ISSS), Pittsburgh, PA, 2016, pp. 1-10.

#### **Book Chapters:**

H. Tann, S. Hashemi, and S. Reda, "Lightweight Deep Neural Network Accelerators Using Approximate SW/HW Techniques," in Approximate Circuits, pp. 289-305. Springer, 2019.

- H. Tann, S. Hashemi, and S. Reda, "Approximate Computing for Iris Recognition Systems," in Approximate Circuits, pp. 331-348. Springer, 2019.

- 3. S. Hashemi, H. Tann, and S. Reda, "Approximate Logic Synthesis Using Boolean Matrix Factorization", in Approximate Circuits, pp. 141-154. Springer, 2019.

#### **Technical Report**

H. Tann, S. Hashemi, S. Reda, "Flexible Deep Neural Networks Processing," arXiv Technical Report, 2018.

#### Acknowledgements

This thesis would not have been possible without the inspirations, support and mentoring from many kind individuals, for whom I am forever grateful. First and foremost, I would like to express my immense gratitude to my advisor and mentor, Prof. Sherief Reda, for his guidance, support and insights. I would also like to thank Prof. Jacob Rosenstein and Prof. Rodrigo Fonseca for being on my defense committee and taking the time to review my thesis.

I am extremely thankful for the fruitful collaborations with all my co-authors, Prof. Iris Bahar, Prof. Jacob Rosenstein, Dr. Soheil Hashemi, Heng Zhao, Francesco Buttafuoco, Chris Arcadia, Nicholas Anthony, Dr. Kumud Nepal, my advisor Prof. Sherief Reda, and many others. My work would not have been possible without them. Specifically, I would like to thank Dr. Soheil Hashemi for being an incredible collaborator and friend.

I would like to thank all my friends at Brown, who made my time here a wonderful one. Thank you to all my friends and colleagues in SCALE lab: Kapil Dev, Xin Zhan, Reza Azimi, Onur Ulusel, Sofiane Chetoui, Farnaz Nouraei, Marina Hesham, Abdelrahman Ibrahim, Abdelrahman Hussein and many others for always making the lab a fun place to be at. Thank you Pratistha Shakya, Chen Lin and the Khmer Student Association for fun parties and gatherings.

I would like to thank Yicheng Shao (Dora) for the years of support, encouragements, insightful discussions, and many unforgettable memories.

Last but not least, I would like to thank my parents, Toumneup Tann and Mouyly Taing, and my siblings for their unwavering support and love. I have learned a lot from them. Without them, none of what I achieved today would be possible.

The research in this thesis is partially supported by NSF grants 1420864, 1814920, and DARPA W911NF-18-2-0031.

Abstract of "Hardware-Software Co-design of Resource-Efficient Deep Neural Networks" by Hokchhay Tann, Ph.D., Brown University, May 2019

The unprecedented success of deep learning technology has elevated the state-of-the-art accuracy performance in many application domains such as computer vision and voice recognition. At the same time, typical Deep Neural Network (DNN) models used in deep learning contain hundreds of millions of parameters and require billions of expensive floating-point operations to process each input. The large storage and computational overheads severely limit DNN's applicability on resource-constrained systems such as mobile and embedded platforms.

Recently, a large number of resource optimization techniques and dedicated hardware architectures have been proposed to alleviate these overheads. The principal observation enabling such optimization approaches stems from the inherent error-resilient property of DNNs, where approximation-induced accuracy loss can be potentially recovered through retraining or finetuning. In addition, applications deploying DNNs in their processing pipeline tend to be resilient to small inaccuracies in the output produced by DNNs. With the growing importance of the field of machine learning and the increasing number of embedded systems, the success of DNN approximation techniques would be critical to enable resource-efficient operations.

This thesis makes several contributions toward advancing the progress of DNN inference on embedded platforms. First, we introduce design methodologies to reduce the hardware complexities of DNN models and propose light-weight approximate accelerators that can efficiently process these models. Our methodologies include analysis and novel training algorithms for a spectrum of data precisions ranging from fixed-point, dynamic fixed point, powers-of-two to binary data precision for both the weights and activations of the models. We demonstrate custom hardware accelerator designs for the various data precisions which achieve low-power and low-latency while incurring insignificant accuracy degradation. To boost the accuracy of the proposed light accelerators, we describe ensemble processing techniques that use an ensemble of light-weight DNN accelerators to achieve the same or better accuracy than the original floating-point accelerator. We also introduce two flexible runtime strategies, which enable significant savings in DNN inference latency. Our methodologies are flexible in that they allow for dynamic adaptation between the quality of results (QoR) and execution runtime. First, we present a novel dynamic configuration technique that permits adjustments in the number of channels in the network depending on response time, power, and accuracy targets. Our second runtime technique enables flexible inference for DNNs ensembles, which is a popular and effective method to boost the inference accuracy.

Next, we showcase our DNN design methodologies using an end-to-end iris recognition application. Here, we propose a resource-efficient end-to-end iris recognition flow, which consists of FCN-based segmentation, contour fitting, followed by Daugman normalization and encoding. To obtain accurate and efficient FCN architectures, we introduce a SW/HW co-design methodology, where we propose multiple novel FCN models. Incorporating each model into the end-to-end flow, we show that the recognition rates of our end-to-end pipelines outperform the previous state-of-the-art on the two datasets evaluated. To further simplify the models for efficient inference, we quantize the weights and activations of the models to dynamic fixed-point (DFP) format and propose a DFP accelerator. We realize our HW/SW co-design pipeline on an embedded FPGA platform.

Finally, we extend our work to emerging computing paradigms for machine learning by introducing a novel methodology for a chemical-based single-layer neural network. We propose a parallel encoding scheme which simultaneously represents multiple bits in microliter-sized chemical mixtures. While the demonstration is still limited in scale, we consider this as a first step to building computing systems that can complement electronic systems for applications in ultra-low-power systems and extreme environments.

## Contents

| Vi | tae          |                                                              | iv  |  |  |

|----|--------------|--------------------------------------------------------------|-----|--|--|

| A  | cknov        | vledgments                                                   | vii |  |  |

| 1  | Introduction |                                                              |     |  |  |

|    | 1.1          | Problem Characterization                                     | 1   |  |  |

|    | 1.2          | Major Thesis Contributions                                   | 4   |  |  |

| 2  | Bac          | kground                                                      | 8   |  |  |

|    | 2.1          | Deep Neural Networks                                         | 8   |  |  |

|    | 2.2          | Hardware-Software Co-design of Deep Neural Networks          | 12  |  |  |

| 3  | Har          | dware-Software Co-design of Deep Neural Network Accelerators | 15  |  |  |

|    | 3.1          | Introduction                                                 | 15  |  |  |

|    | 3.2          | Data Precision Options                                       | 17  |  |  |

|    | 3.3          | Hardware Accelerator Designs                                 | 20  |  |  |

|    | 3.4          | Training For Low Precision Networks                          | 23  |  |  |

|    | 3.5          | Boosting Accuracy with Ensemble Processing                   | 27  |  |  |

|    | 3.6          | Experimental Results                                         | 28  |  |  |

|    | 3.7          | Conclusion                                                   | 32  |  |  |

| 4  | Run          | time-Flexible Deep Neural Networks Processing                | 34  |  |  |

|    | 4.1          | A Dynamically Configurable DNN Design                        | 35  |  |  |

|   |                             | 4.1.1                                                                                              | Introduction                                                                   | 35                                                                                                                     |

|---|-----------------------------|----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                             | 4.1.2                                                                                              | Background                                                                     | 36                                                                                                                     |

|   |                             | 4.1.3                                                                                              | Methodology                                                                    | 37                                                                                                                     |

|   |                             | 4.1.4                                                                                              | Runtime Methodology                                                            | 42                                                                                                                     |

|   |                             | 4.1.5                                                                                              | Experiments                                                                    | 48                                                                                                                     |

|   |                             | 4.1.6                                                                                              | Experimental Setup                                                             | 48                                                                                                                     |

|   |                             | 4.1.7                                                                                              | Conclusions                                                                    | 59                                                                                                                     |

|   | 4.2                         | A Flex                                                                                             | tible Processing Strategy for DNN Ensembles                                    | 59                                                                                                                     |

|   |                             | 4.2.1                                                                                              | Introduction                                                                   | 59                                                                                                                     |

|   |                             | 4.2.2                                                                                              | Related Works                                                                  | 61                                                                                                                     |

|   |                             | 4.2.3                                                                                              | Methodology                                                                    | 62                                                                                                                     |

|   |                             | 4.2.4                                                                                              | Experimental Results                                                           | 66                                                                                                                     |

|   | 4.3                         | Conclu                                                                                             | usion                                                                          | 68                                                                                                                     |

|   |                             |                                                                                                    |                                                                                |                                                                                                                        |

| 5 | Res                         | ource-F                                                                                            | fficient Fully Convolutional Networks for Iris Recognition An-                 |                                                                                                                        |

| 5 |                             | ource-E<br>ation                                                                                   | fficient Fully Convolutional Networks for Iris Recognition Ap-                 | 69                                                                                                                     |

| 5 |                             | ation                                                                                              | Afficient Fully Convolutional Networks for Iris Recognition Ap-         uction | <b>69</b><br>69                                                                                                        |

| 5 | plic                        | ation<br>Introdu                                                                                   |                                                                                |                                                                                                                        |

| 5 | <b>plic</b><br>5.1          | ation<br>Introdu                                                                                   | uction                                                                         | 69                                                                                                                     |

| 5 | <b>plic</b><br>5.1          | ation<br>Introdu<br>Backg                                                                          | uction                                                                         | 69<br>72                                                                                                               |

| 5 | <b>plic</b><br>5.1          | ation<br>Introdu<br>Backg<br>5.2.1                                                                 | uction                                                                         | 69<br>72<br>73                                                                                                         |

| 5 | <b>plic</b><br>5.1          | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3                                               | uction                                                                         | 69<br>72<br>73<br>75                                                                                                   |

| 5 | <b>plic</b> :<br>5.1<br>5.2 | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3                                               | uction                                                                         | 69<br>72<br>73<br>75<br>76                                                                                             |

| 5 | <b>plic</b> :<br>5.1<br>5.2 | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3<br>Propos                                     | uction                                                                         | 69<br>72<br>73<br>75<br>76<br>78                                                                                       |

| 5 | <b>plic</b> :<br>5.1<br>5.2 | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3<br>Propos<br>5.3.1                            | uction                                                                         | <ul> <li>69</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>78</li> <li>79</li> </ul>                         |

| 5 | <b>plic</b> :<br>5.1<br>5.2 | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3<br>Propos<br>5.3.1<br>5.3.2                   | uction                                                                         | 69<br>72<br>73<br>75<br>76<br>78<br>79<br>82                                                                           |

| 5 | <b>plic</b> :<br>5.1<br>5.2 | ation<br>Introdu<br>Backg<br>5.2.1<br>5.2.2<br>5.2.3<br>Propos<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | uction                                                                         | <ul> <li>69</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>78</li> <li>79</li> <li>82</li> <li>85</li> </ul> |

|   |      | 5.4.2    | FCN Processing Components                             | 91  |

|---|------|----------|-------------------------------------------------------|-----|

|   |      | 5.4.3    | Hardware Accelerator Architecture                     | 92  |

|   | 5.5  | Experi   | mental Results                                        | 95  |

|   |      | 5.5.1    | Experimental Setup                                    | 95  |

|   |      | 5.5.2    | Recognition Performance Evaluations and Comparisons   | 95  |

|   |      | 5.5.3    | Runtime Performance and Hardware Acceleration Speedup | 100 |

|   | 5.6  | Conclu   | usion                                                 | 102 |

| 6 | Co-l | Design ' | Techniques for Chemical-based Neural Classifier       | 104 |

|   | 6.1  | Introdu  | uction                                                | 104 |

|   | 6.2  | Propos   | sed Chemical Computing Methodology                    | 106 |

|   |      | 6.2.1    | Encoding Data in Chemical Mixtures                    | 106 |

|   |      | 6.2.2    | Computing with Chemical Mixtures                      | 108 |

|   |      | 6.2.3    | Reading the Results of Chemical Mixture Computations  | 111 |

|   | 6.3  | Systen   | n Development                                         | 112 |

|   |      | 6.3.1    | Experimental Setup                                    | 112 |

|   | 6.4  | Experi   | ments & Results                                       | 113 |

|   |      | 6.4.1    | Robustness Simulation                                 | 114 |

|   |      | 6.4.2    | MNIST Image Classification                            | 115 |

|   |      | 6.4.3    | Performance Evaluation                                | 116 |

|   | 6.5  | Conclu   | usion                                                 | 118 |

| 7 | Sum  | imary o  | of Dissertation and Possible Future Directions        | 119 |

|   | 7.1  | Summ     | ary of Results                                        | 120 |

|   | 7.2  | Potent   | ial Research Extensions                               | 123 |

|   | Bibl | iograpł  | <b>1</b> y                                            | 124 |

# **List of Figures**

| 2.1 | The structure of a neuron (perceptron)                                                                                                                                                                                                                                                                                                | 9  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | The structure of a typical DNN                                                                                                                                                                                                                                                                                                        | 9  |

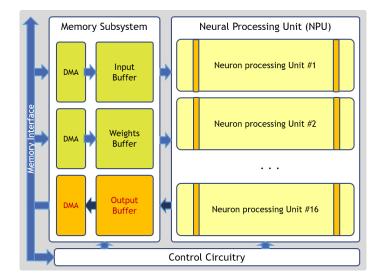

| 3.1 | The hardware architecture of our accelerator.                                                                                                                                                                                                                                                                                         | 20 |

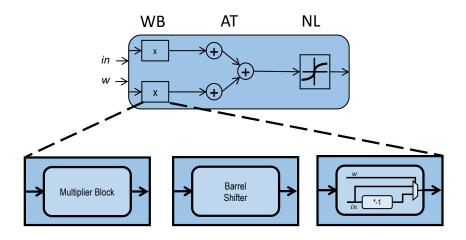

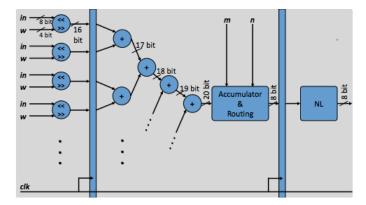

| 3.2 | Architecture of Neural Processing Unit for uniform fixed-point activations.<br>The pipeline consists of three main blocks: weight block (WB), adder<br>tree (AT), and non-linearity unit (NL). The weight block can be modified<br>according to different weight quantization schemes.                                                | 21 |

| 3.3 | Architecture of Neural Processing Unit for dynamic fixed-point precision.                                                                                                                                                                                                                                                             | 23 |

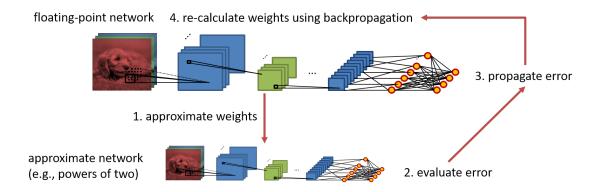

| 3.4 | Training procedure for DNNs with reduced-precision parameters                                                                                                                                                                                                                                                                         | 24 |

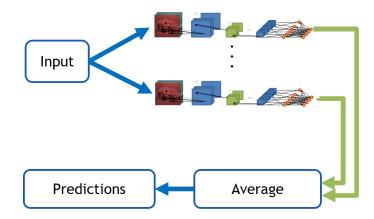

| 3.5 | Ensemble Processing                                                                                                                                                                                                                                                                                                                   | 28 |

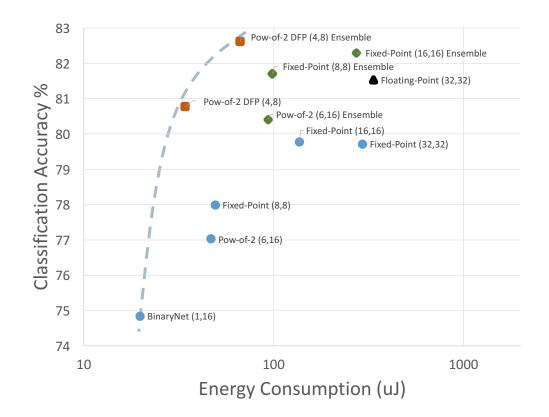

| 3.6 | The Pareto Frontier plot of the evaluated design points for CIFAR-10 dataset. The X-axis is shown in logarithmic scale to cover the large energy range of all the designs. Here, the black point indicates the initial 32-bit floating-point design.                                                                                  | 31 |

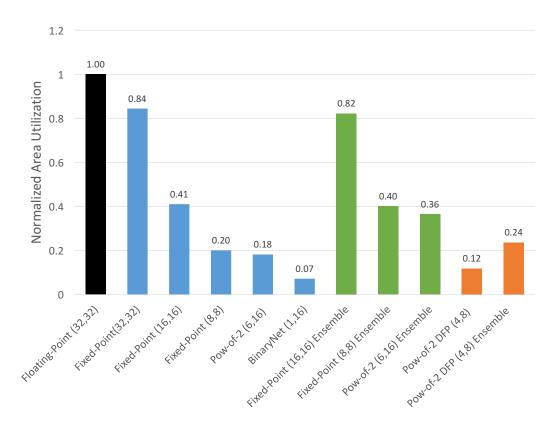

| 3.7 | Accelerator area utilization for different precision formats normalized against the 32-bit floating-point reference design.                                                                                                                                                                                                           | 32 |

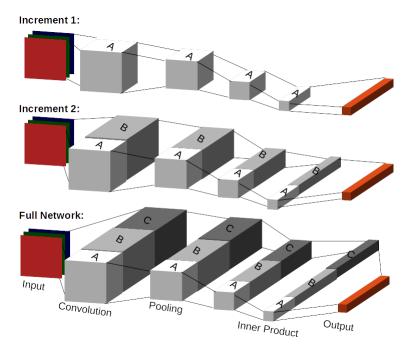

| 4.1 | Illustration of Incremental Training on a typical DNN                                                                                                                                                                                                                                                                                 | 38 |

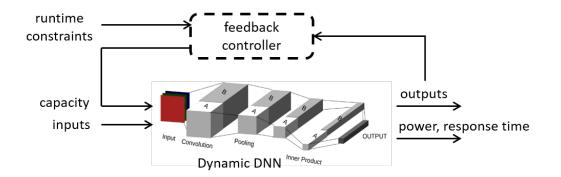

| 4.2 | Dynamic adjustment of DNN capacity using feedback controllers as im-<br>plemented in the proposed constrained design approach. For real time con-<br>straints, the controller monitors the response time and power consumption<br>of the DNN and adjusts its capacity based on the measurements and the<br>target runtime constrains. | 43 |

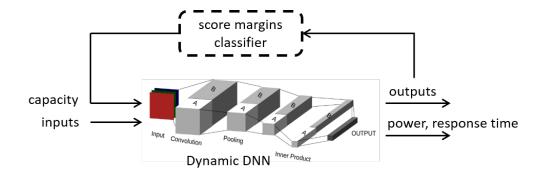

| 4.3 | Dynamic adjustment of DNN capacity using score margin classifiers as implemented in the proposed opportunistic approach. The score margin unit scales down the DNN to save energy as long as accuracy is not compromised.                                                                                                             | 44 |

|     |                                                                                                                                                                                                                                                                                                                                       | 17 |

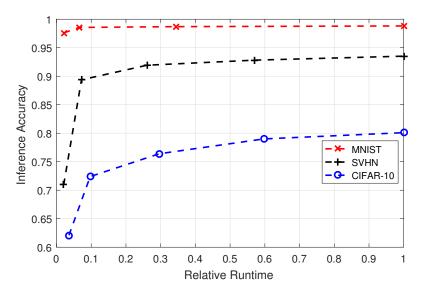

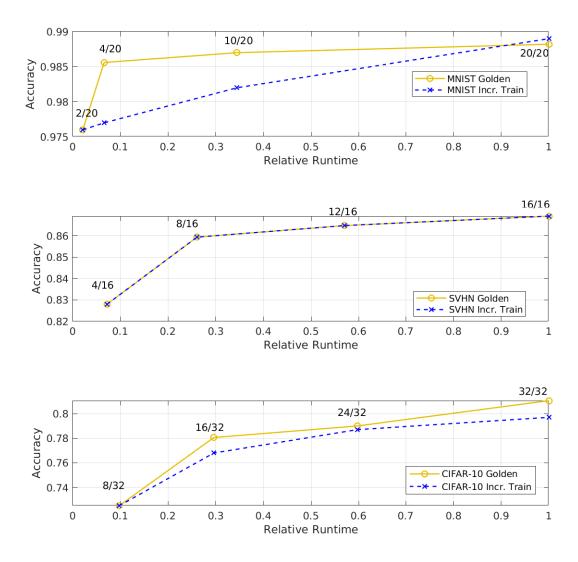

| 4.4  | Inference accuracy of golden model in validation set versus relative net-<br>work runtime in forward pass.                                                                                                                                                                                                                                                                                     | 46 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

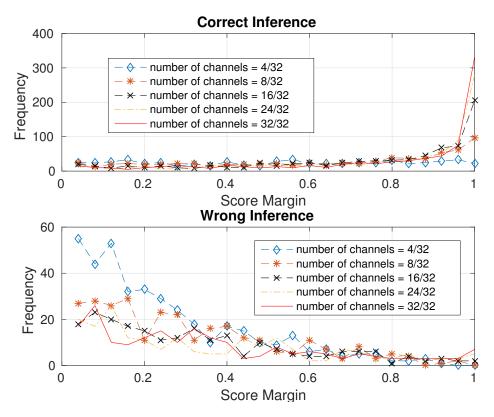

| 4.5  | Histogram for top two class scores margin for correct inference (top) and wrong inference (bottom) for CIFAR-10 dataset. The number of channels $(x/y)$ shows the ratio of number of channels in the first layer of the network in use (x) and that of the full network (y). This ratio is identical for all layers except the final layer.                                                    | 48 |

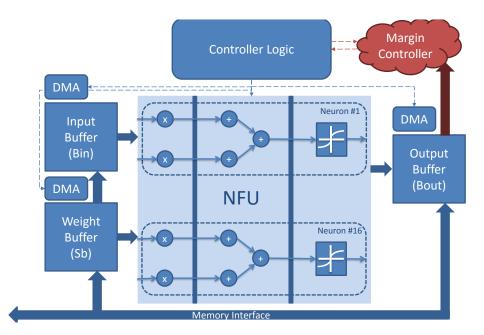

| 4.6  | The custom HW implemented in our work                                                                                                                                                                                                                                                                                                                                                          | 49 |

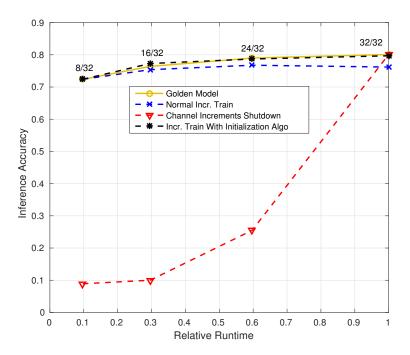

| 4.7  | Comparison of inference accuracy on CIFAR-10 validation set for golden model, incremental training, channel increments shutdown and incremental training with initialization from Section 8. Relative runtime is the ratio of the forward-pass runtime to that of the full network. The two numbers displayed at each datapoint (x/y) shows the number of channels as explained in Figure 4.5. | 53 |

| 4.8  | Test set inference accuracy versus network relative runtime for MNIST (top), SVHN (middle), and CIFAR-10 (bottom). The two numbers $(x/y)$ at each data point have the same representation as Figure 4.5.                                                                                                                                                                                      | 54 |

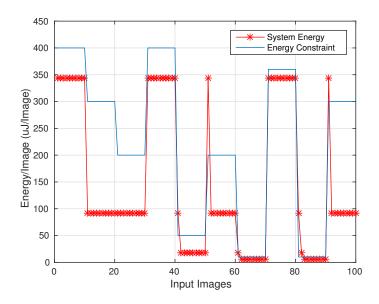

| 4.9  | Comparison of network energy adjusts with the imposed energy budget over time running MNIST tesebench.                                                                                                                                                                                                                                                                                         | 57 |

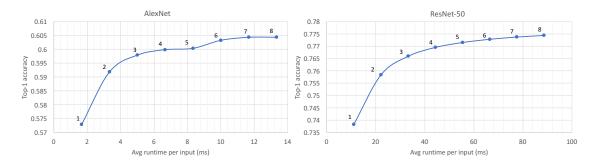

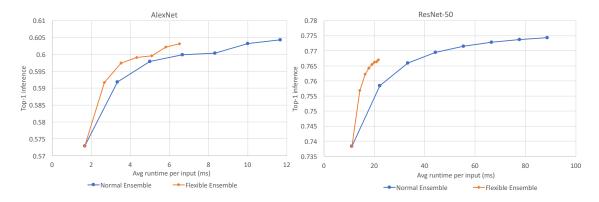

| 4.10 | Inference accuracy versus average runtime per input for AlexNet and ResNet-<br>50 for DNN ensembles on ImageNet validation set. Each data label shows<br>the number of networks in the ensemble. Runtime results are based on a<br>system with a Nvidia Titan Xp GPU                                                                                                                           | 62 |

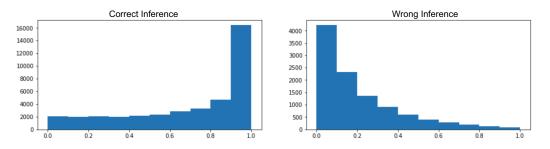

| 4.11 | Score Margins histograms for correct and wrong top-1 inference for AlexNet.<br>The x-axis shows the score margin, and the y-axis shows the number of<br>samples in each score margin bin.                                                                                                                                                                                                      | 65 |

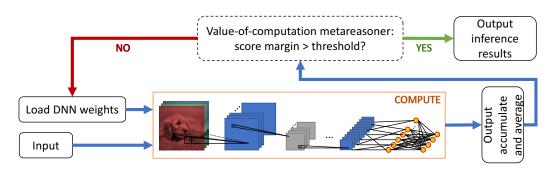

| 4.12 | Execution flow for flexible DNN ensemble processing.                                                                                                                                                                                                                                                                                                                                           | 65 |

| 4.13 | Inference accuracy versus average runtime per input for AlexNet and ResNet-<br>50 for normal and flexible ensemble execution. Runtime results are based<br>on a system with a Nvidia Titan Xp GPU.                                                                                                                                                                                             | 67 |

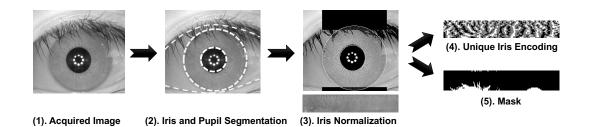

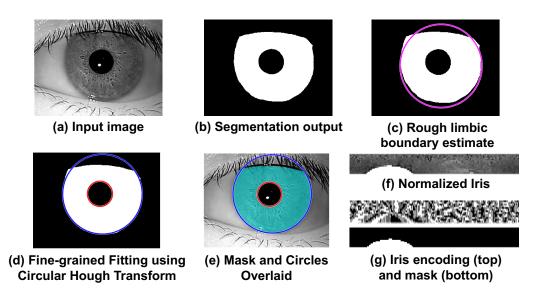

| 5.1  | Typical processing pipeline for iris recognition applications based on Daug-<br>man [19].                                                                                                                                                                                                                                                                                                      | 73 |

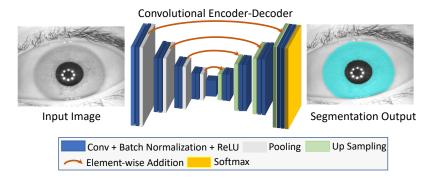

| 5.2  | Architecture for Encoder-Decoder Fully Convolution Networks with skip connections for semantic segmentation.                                                                                                                                                                                                                                                                                   | 75 |

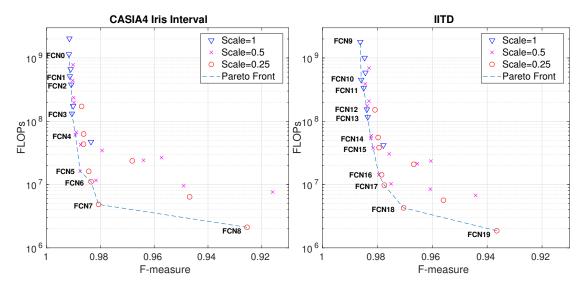

| 5.3  | F-measure segmentation accuracy and computational complexity of can-<br>didate FCN models on CASIA Iris Interval V4 and IITD datasets. The<br>models use 32-bit floating point for both weights and activations. The<br>scales refer to the ratio of the model input dimensions to the original<br>image resolutions from the datasets. Smaller resolution inputs can sig-<br>nificantly reduce the computational complexity of the models. We label<br>models which make up the Pareto fronts as FCN0-FCN8 for CASIA4 and<br>FCN9-FCN19 for IITD.                         | 83  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Processing pipeline for contour fitting, normalization and encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 87  |

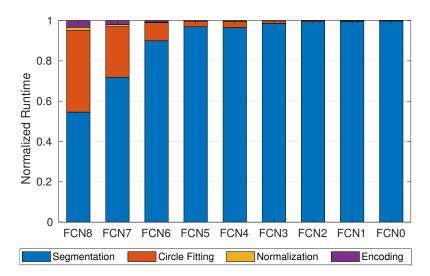

| 5.5  | FCN-based iris recognition pipeline runtime breakdown for floating-point FCN0–FCN8 models from CASIA Interval V4 Pareto front in Figure 5.3. From left to right, the FCN models are arranged in increasing computational complexity. Results are based on floating-point FCN models                                                                                                                                                                                                                                                                                        | 90  |

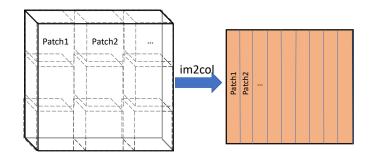

| 5.6  | Image to column operation for convolution layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92  |

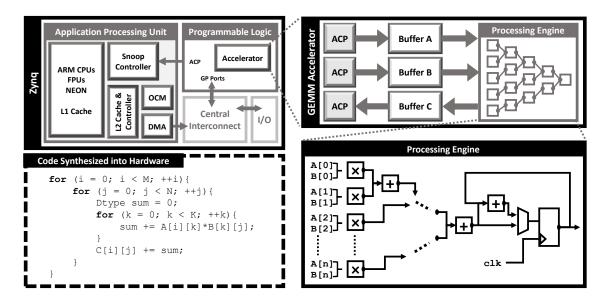

| 5.7  | Overall system integration and the hardware accelerator module for the <i>GEMM</i> unit. The code representing the operations of the hardware module is shown in the bottom left, where A and B are the multiplicant and multiplier matrices, and C is the resulting output matrix. For DFP version of the accelerator, A and B are 8-bit, and C is 16-bit. A, B and C are all 32-bit floats for the floating-point version. The accelerator module is connected to the Zynq Processor Unit via the Accelerator Coherency Port (ACP).                                      | 93  |

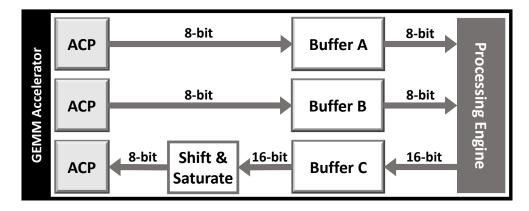

| 5.8  | A closer look at the data paths of the buffers in the DFP accelerator unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 94  |

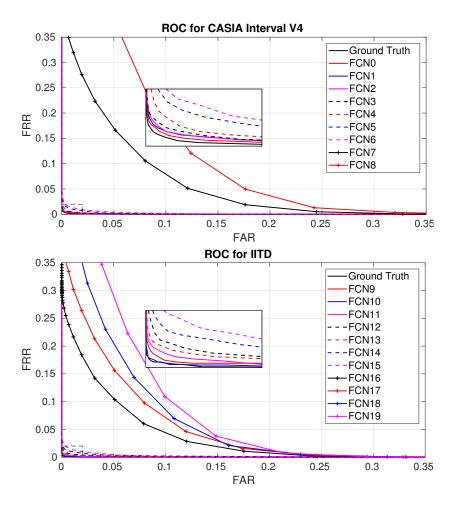

| 5.9  | Receiver Operating Characteristic (ROC) curves of FCN-based iris recog-<br>nition pipelines with ground truth segmentation and different floating-<br>point FCNs models for CASIA Interval V4 and IITD datasets. In the leg-<br>end of each dataset, the FCN models are arranged in increasing FLOPs<br>from bottom to top. The zoom-in axis range is [0 0.02] for both x and y<br>directions                                                                                                                                                                              | 97  |

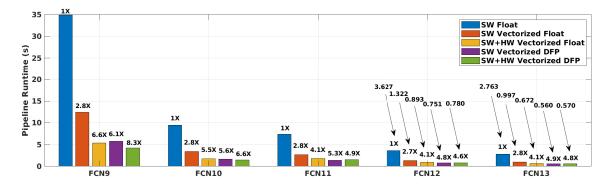

| 5.10 | Runtime results for end-to-end FCN-based iris recognition pipelines based<br>on different FCN segmentation models for the IITD dataset. Five plat-<br>form configurations are reported: pure none-vectorized floating-point soft-<br>ware (SW Float), vectorized float-point and fixed-point software using<br>ARM NEON instructions (SW Vectorized Float, SW Vectorized DFP) and<br>hardware accelerated with floating-point and DFP acceleerators (SW+HW<br>Vectorized Float, SW+HW Vectorized DFP). The speedup relative to SW<br>Float is reported on top of each bar. | 100 |

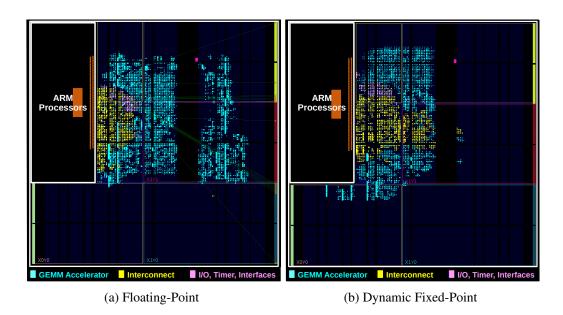

| 5.11 | FPGA floorplans of our synthesized accelerators and system modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 102 |

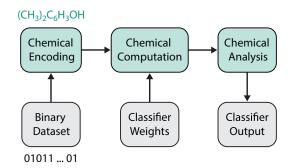

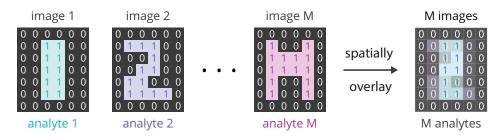

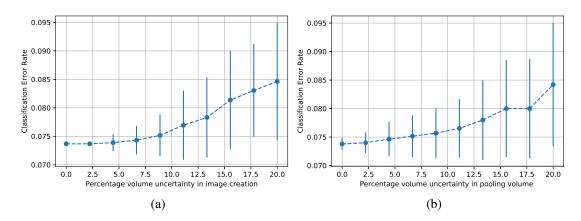

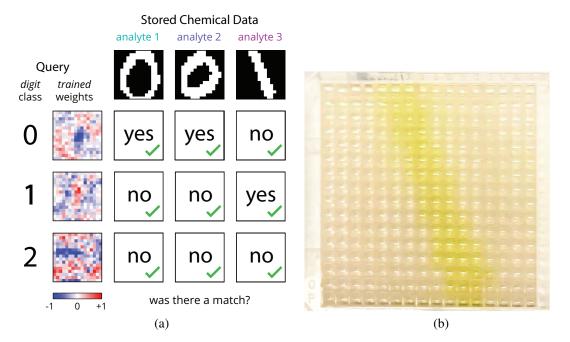

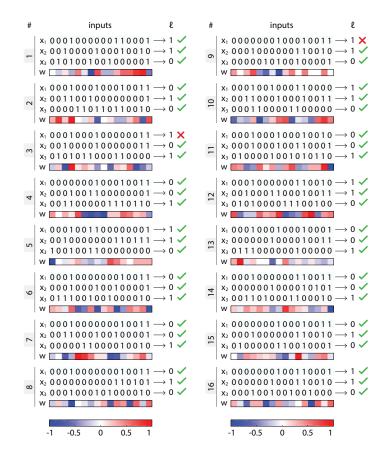

6.1 A conceptual block diagram of the chemical computation scheme. Binary datasets are encoded into discretized mixtures of chemicals. Computations can be performed on these chemical mixtures through quantitative sampling, based on the desired classifier's weights, and mixing of their contents. The computation output is initially still in the chemical domain, and can be assessed using analytical chemistry techniques. Figure from 106 Data is stored in isolated wells containing quantitative chemical mixtures. 6.2 The concentrations of these chemicals reflect the values of the binary input data. Each bit address in the input data is assigned to one grid location on a microplate, while the value of each bit is encoded in the concentration of a particular chemical compound at that position. Multiple datasets can be simultaneously stored in the same fluid containers by using multiple A schematic of the proposed chemical computation procedure, as im-6.3 plemented for pattern classification. All spatially concurrent chemical datasets (x) are operated on in parallel by a single weight matrix (w), whose values are realized as volumetric fluid transfers. Since weights can be positive and negative ( $w_i \in [-1, 1]$ ), a pool for each polarity is made. Each pool is analyzed by liquid chromatography to measure the concentrations of each analyte species. The differential concentration of each analyte is calculated in post-processing and used to determine the appropriate label for the input data. Figure from Arcadia *et al.* [6]. . . . . 109 An overview of the experimental setup and data flow used for these exper-6.4 iments. Weight matrices were trained in simulation and then converted, along with test data, into sequences of pipetting instructions for a robotic liquid handler. Analytes were dispensed into a 384-well microplate to form the chemical dataset and then collected in volume fractions corresponding to the classifier weight matrix. The outputs were analyzed by HPLC to produce class labels. Figure from Arcadia et al. [6]. . . . . . . . 112 Single-layer neural network classification simulation results. Figure (a) 6.5 shows the classification error introduced from the varying uncertainties in image creation portion while assuming the volumetric multiply-accumulate and HPLC readings are assumed to be exact. For Figure (b), the volume uncertainty for image creation was fixed at 0.05 while varying the uncertainties in the multiply-accumulate pooling volumes. The HPLC concentration reading was assumed to be exact. For each data point in both figures, the mean and standard deviation are computed from a trial of 100

# **List of Tables**

| 3.1 | Classification accuracy, inference time, and energy cost for CIFAR-10 and<br>ImageNet benchmark DNNs based on different numerical representation<br>and ensembling. Ensemble deployment uses two DNNs in the inference.<br>Accuracy results show Top-1 performance and Top-5 in parentheses for<br>ImageNet benchmark. | 30 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | The hardware implementation characteristics of different arithmetic and bit-widths.                                                                                                                                                                                                                                    | 50 |

| 4.2 | Breakdown of hardware implementation characteristics of different com-<br>ponents                                                                                                                                                                                                                                      | 51 |

| 4.3 | Benchmark Networks Architecture Descriptions.                                                                                                                                                                                                                                                                          | 52 |

| 4.4 | Mean energy cost (E) and processing time (T) per input image when differ-<br>ent fractions of the each networks are deployed using our custom hardware<br>accelerator.                                                                                                                                                 | 55 |

| 4.5 | Mean energy cost (E) and processing time (T) per input image when differ-<br>ent fractions of the each networks are deployed using Nvidia Jetson TX1<br>GPU board. Input images are fed into the network one at a time                                                                                                 | 56 |

| 4.6 | Additional storage requirements normalized to the original network when<br>the system is allowed to store multiple weights network                                                                                                                                                                                     | 57 |

| 4.7 | Optimal number of retraining increments for each network and fractions of active channels in each layer for each increment (score margin threshold in parentheses).                                                                                                                                                    | 58 |

| 4.8 | Inference Accuracy (in parenthesis is the accuracy of the golden model<br>for network with the same size as the increment) and energy cost for each<br>increment in incremental training.                                                                                                                              | 58 |

| 4.9 | Energy savings and accuracy drops for the dynamic configuration normal-<br>ized to the golden result.                                                                                                                                                                                                                  | 59 |

| 5.1 | Proposed baseline FCN architecture. Each convolution layer (CONV) is<br>followed by Batch Normalization and ReLU activation layers. Transposed<br>convolution layer (TCONV) is followed by ReLU activation layer. The<br>arrows denote the skip connections, where the outputs of two layers are<br>added together element-wise before passing to the next layer. Variable<br>N denotes the number of feature maps per layer, which is varied among<br>different designs explored. | 80  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2 | Segmentation Accuracy Comparison to Previous Works                                                                                                                                                                                                                                                                                                                                                                                                                                 | 84  |

| 5.3 | Descriptions of FCN architectures and their computational complexities (MFLOPs) which achieve top segmentation accuracy among all models explored in Figure 5.3 for CASIA Interval V4 and IITD datasets. As in Table 5.1, each CONV layer is followed by Batch Normalization and ReLU, and TCONV is followed by ReLU. FS denotes the filter size, and the skip connections are represented by the arrows.                                                                          | 85  |

| 5.4 | Runtime profile for floating-point FCN inference using the onboard CPU.                                                                                                                                                                                                                                                                                                                                                                                                            | 90  |

| 5.5 | Equal Error Rate (EER) and segmentation accuracy ( $\mathcal{F}$ -measure) comparison between previous approaches, our FCN-based pipeline and groundtruth (GT). In each dataset, FCN models are floating-point based and arranged in increasing FLOPs and $\mathcal{F}$ -measure from top to bottom.                                                                                                                                                                               | 98  |

| 5.6 | Equal Error Rate (EER) and segmentation accuracy ( $\mathcal{F}$ -measure) compar-<br>ison between the groundtruth (GT), floating-point, and DFP FCN-based<br>recognition pipelines using the IITD dataset.                                                                                                                                                                                                                                                                        | 99  |

| 5.7 | Utilization of FPGA Resources for Look-up Tables (LUT), LUT as mem-<br>ory (LUTRAM), Flip-Flop Registers, Block RAM (BRAM), Digital Sig-<br>nal Processing units (DSP), and Global Clock Buffers (BUFG)                                                                                                                                                                                                                                                                            | 101 |

| 6.1 | Computational cost of classifying $M$ binary inputs, each containing $N$ bits, in a traditional versus volumetric neuron $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                               | 108 |

### Chapter 1

### Introduction

### **1.1 Problem Characterization**

Machine learning has become an integral part of many systems we interact with. From data centers to embedded devices, machine learning models are deployed to enable various services such as language translations, voice recognition, and recommendation engines. With the recent breakthroughs in deep learning [56, 32], we are capable of solving ever more complex tasks, many of which were not previously possible. The ability to automatically learn important features from large datasets distinguishes deep learning models, also known generally as deep neural networks (DNNs), from previous machine learning techniques, which rely on handcrafted feature extractors. In order to capture essential features and their underlying relationships from large and complex datasets, state-of-the-art DNNs typically consists of hundreds of millions of trainable parameters, hyperparameters and require millions of expensive computations for each input.

The success in deep learning has been possible in part due to the performance leaps

achieved in modern computing systems. As accurately predicted by Gordon Moore in 1965, Moore's law states that the number of transistors in dense integrated circuits roughly doubles every 18 months [67]. This is due to the continual downsizing of the transistor area, which improves the circuit performance by allowing for higher switching frequency. In addition, the observation from Robert Dennard in 1974, known as the Dennard scaling, stated that with the shrinking of the transistor feature size, the operating voltage and current would be downscaled proportionally and that the power density would remain constant [21]. Combining of Moore's Law and Dennard scaling, this meant that the performance per watt of integrated circuits would double every 18 months paving way for an incredible semiconductor roadmap. However, more recently, we have reached the end of Dennard scaling and soon Moore's Law. In order to keep up the momentum, the industry and academic research have looked for other directions such as parallelized multicore systems and building more specialized circuits, i.e. accelerators and Application-Specific Integrated Circuits (ASIC), for various tasks and integrate them as a system on a chip (SoC) [22, 23].

In addition, as we target more and more challenging tasks, it is expected that the complexities of DNN models will continue to grow dramatically. In order to continue the progress in deep learning, efficient high-performance computing systems and methodologies are among the essential components. This need is evidenced in recent work such as neural architecture search [104], which deployed 800 Graphics Processing Units (GPU) concurrently. For this reason, a thriving field of research in both academia and industries focuses on designing specialized, efficient hardware architectures to support the immense computational requirements of DNNs. Some of the popular systems currently deployed to train and run large DNNs models from industries include the deep-learning tailored GPUs, Tensor Processing Unit (TPU) [51] and Fields-Programmable Gate Array (FPGA).

Another line of research focuses on the deployments of DNN models in more resource-

constrained environments, which are mobile and embedded systems. With the ubiquity of these platforms, they have become popular target systems for many deep learning applications. However, these systems are often battery-powered with limited computational resources and strict power budgets making the deployments of large DNN models challenging. This problem has motivated many studies which focus on designing specialized, efficient hardware architectures and software-hardware co-design approaches to support the computational need of DNNs while simultaneously meeting the system constraints [15, 16, 31, 99]. A large number of software-hardware co-design approaches were proposed to reduce the complexities of DNN models through sparsification [60], bit-width reduction [34], as well as exploring more efficient model architectures [44, 47]. Others have proposed low-power, small-footprint accelerator designs which can support many of the simplified DNNs models [15, 16, 100, 35]. Collectively, these various techniques have shown promising results in achieving an orders-of-magnitude reduction in the number of arithmetic operations, runtimes, and power requirements.

The impressive improvements from the proposed optimization techniques are often realized by trading off small accuracy loss of the models for large savings in computational overhead. However, this accuracy loss is often measured through certain test sets with isolated DNNs. In many end-to-end applications, DNNs are often just one of the components in the processing pipeline. Thus, the isolated accuracy loss measurements may not reflect the true performance of the optimization methodologies on the end-to-end applications. It is vitally important to also capture the impacts of proposed optimization techniques on the end-to-end performance of the applications. As evidenced in the previous work [37, 90], such end-to-end evaluation can also provide additional insights, which simplify the DNN models.

Finally, while semiconductor-based computing systems have driven the breakthroughs in deep learning, alternative computing paradigms, which could potentially offer more flexibility as well as efficiency in computation may be necessary to help drive the progress forward. A number of emerging technologies have been explored such as in-memory computations, quantum computing, and chemical-based computing. These alternative paradigms may help bring deep learning to new applications, where semiconductor-based systems are unsuitable. Next, we provide a summary of the contributions made in this thesis.

#### **1.2 Major Thesis Contributions**

In this section, we outline the major contributions made in this thesis with regards to the explorations of efficient DNNs design methodologies and accelerations as well as the emerging chemical computing domain.

1. Hardware-Software Co-design of Deep Neural Network Accelerators: In Chapter 3, we propose a hardware-software co-design methodology targeting DNN accelerations to achieve low-power, low-latency inference with insignificant degradation in accuracy performance. Our goal is to devise light approximate DNN accelerators that use fewer hardware resources while incurring negligible accuracy loss. In order to simplify the hardware requirements, we first perform a detailed analysis of a broad range of data representation formats ranging from floating point to fixed point, dynamic fixed point, powers-of-two, and binary weights and activations. To compensate for accuracy loss due to the limited bit-precisions, we employ learning technique which performs quantization-aware fine-tuning of the DNN parameters. In addition, we show how to fine-tune a low-precision DNN using student-teacher learning to improve accuracy performance in a similar manner to knowledge distillation [39]. Our technique does not require architectural change for the network.

We also describe how to utilize an ensemble of low-precision networks to boost classification accuracy while still allowing large energy savings. We demonstrate the effectiveness of our DNN accelerators through two well-known state-of-the-art and demanding datasets, namely CIFAR-10 and ImageNet, with well-recognized network architectures for our experiments. Our light DNN accelerators provide dramatic savings in energy consumption in comparison to a baseline floating-point accelerator.

2. Runtime-Flexible Deep Neural Networks Processing: The hardware-software codesign technique proposed in Chapter 3 focuses on the design-time aspect of DNN optimization. Once the fine-tuning process is completed, the runtime and accuracy of the model are fixed. While the technique significantly simplifies the DNN models, fixed accuracy loss and runtime may not be desirable or efficient for applications with varying real-time constraints such as recommendation systems. To enable runtime flexibility, we propose in Chapter 4, two runtime trade-off strategies which aim to lower the average inference latency of DNN models, while maintaining minimal impact on accuracy performance. Our techniques are flexible in that they allow for dynamic adaptation between the quality of results (QoR) and execution runtime. First, in Section 4, we propose a runtime-configurable DNN design and incremental training strategy, which allow parts of the models to be shut down at runtime to reduce computational cost. We evaluate our proposed methods using two different platforms: a low-power embedded GPU and a custom ASIC-based hardware accelerator design, which uses an industrial-strength tool flow and a 65 nm technology library. Next, in Section 4.2, we propose runtime trade-off strategies for DNN ensembles, which is a popular and effective technique to boost inference accuracy performance. We demonstrate the effectiveness of the technique on wellknown models, which are AlexNet [56] and ResNet-50 [38] using the ImageNet dataset [79].

- 3. Resource-Efficient Fully Convolutional Networks for Iris Recognition Application: In Chapter 4, in order to explore the effects of DNN HW/SW co-design methodologies on an end-to-end application, we propose an iris recognition processing pipeline, which consists of fully convolutional neural network (FCN) based segmentation, contour fitting, followed by Daugman normalization and encoding. To obtain accurate and efficient FCN architectures, we employ HW/SW co-design methodologies as proposed in Chapter 3 while introducing architectural exploration as a first step. In this exploration, we propose multiple novel FCN models and construct a Pareto plot based on their segmentation performance and computational overheads. We then select the most efficient set of models and further optimizing their HW resources by quantizing their weights and activations to 8-bit dynamic fixed-point. We then incorporate each model into the end-to-end flow to evaluate their true recognition performance. Compared to previous works, our FCN architectures require  $50 \times$  fewer FLOPs per inference while setting a new state-of-the-art segmentation accuracy. The recognition rates of our end-to-end pipeline also outperform the previous state-of-the-art on the two datasets evaluated. We then propose a custom dynamic fixed-point accelerator and fully demonstrate the SW/HW codesign realization of our flow on an embedded FPGA platform. In comparison with the embedded CPU, our hardware acceleration achieves up to  $8.3 \times$  speedup for the overall pipeline while using less than 15% of the available FPGA resources.

- 4. A Novel Volumetric Chemical Single-Layer Neural Networks for Parallelized Classifications: We extend our work to emerging computing paradigms for machine learning by introducing a novel methodology for the chemical-based singlelayer neural network (NN) in Chapter 6. We propose a novel encoding technique which simultaneously represents multiple datasets in an array of microliter-scale chemical mixtures. Parallel computations on these datasets are performed as robotic liquid handling sequences, whose outputs are analyzed by high-performance liquid

chromatography. As a proof of concept, we chemically encode several MNIST images of handwritten digits and demonstrate successful chemical-domain classifications of the digits using a volumetric single-layer NN. We additionally quantify the performance of our method with a larger dataset of binary vectors and compare the experimental measurements against predicted results. Paired with appropriate chemical analysis tools, our approach can work on increasingly parallel datasets. We anticipate that related approaches will be scalable to multilayer NNs and other more complex algorithms.

The organization for the remainder of this thesis is as follows. Chapter 2 briefly reviews the basics of DNNs and related works in DNN HW/SW co-design methodologies. Next, Chapter 3 presents our proposed HW/SW co-design techniques aimed at simplifying DNN designs. Chapter 4 introduces our proposed runtime-flexible methodologies and results on well-known benchmarks. Next, in order to explore the impacts of DNN HW/SW co-design methodologies on an end-to-end application, we present an iris recognition pipeline with FCN-based segmentation in Chapter 5. In Chapter 6, we propose and demonstrate novel parallelized single-layer NN classifier in the chemical domain. Finally, Chapter 7 summarizes the results and findings presented in this thesis as well as offering insights for future extensions to this work.

### Chapter 2

### Background

### 2.1 Deep Neural Networks

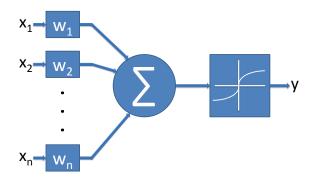

Inspired by the structure of the human brain, deep neural networks (DNNs) are proposed as a family of machine learning models which loosely resembles the connections of the neurons in the brain. At the core of DNNs are the neuron units, which were originally proposed several decades ago. Beginning in the 1940s, the McCulloch-Pitts neuron [66] was proposed, where two binary inputs are fed into a threshold function. This single neuron unit could perform simple logical operations such as AND and OR. Building on top of this model, Frank Rosenblatt [78] proposed the perceptron model, which could take analog values inputs and perform a weighted sum of the inputs before passing the result through a threshold or other kinds of non-linear functions. Figure 2.1 shows structure of the perceptron model, and its operation can be formulated as:

$$y = \mathcal{F}(\sum_{i=0}^{n-1} x_i \cdot w_i + b),$$

Figure 2.1: The structure of a neuron (perceptron).

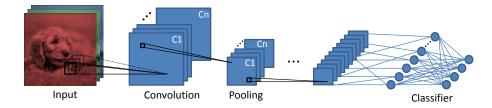

Figure 2.2: The structure of a typical DNN.

where  $x_i$  and  $w_i$  are the *i*-th input feature and weights respectively, b is the bias, and  $\mathcal{F}$  is the non-linear function. In modern DNNs, the perceptron model is used as the core neuron unit, where they are arranged in multiple layers. The weights in DNNs are adjusted as the models learn to perform various tasks. Figure 2.2 shows the organization and connections of layers in a type of DNNs, namely convolutional neural network (CNN). CNNs are typically employed for tasks involving images or videos as inputs. Note that, while there exists many different types of DNNs targeted for tasks from various domains, we focus mainly on CNNs and their variants when referring to DNNs in this thesis.

With the availability of high-performance computing systems and large training datasets, DNNs have recently produced state-of-the-art accuracy performances for many of the most challenging problems in computer vision, such as image classification and object detection. As shown in Figure 2.2, traditional DNN architectures consist of several stacked layers, where each layer gets its input from the previous layer and feeds its output to the next layer. Here, the intermediate values between different layers are called the feature maps. In this approach, each layer consists of a number of channels, where each channel is responsible for implementing a specific feature map filter. Channels within a layer share the inputs from the previous layer while each using a different set of weights.

While there is a broad range of different layers available in the literature, some of the most common types of layers in DNNs include convolutional, pooling, and fully connected layers. More recently, transposed convolution layers, also known as deconvolutional layers, are also becoming prevalent due to their importance in image segmentation and generative adversarial networks (GANs). These layers are typically followed by a non-linear activation function. We briefly describe each layer type below.

- Convolutional Layers: Convolutional layers have multiple filters, where each filter applies a convolution to the input feature maps. In other words, the convolutional layer performs a weighted sum on a region of the input features. The number of filters directly translates into the number of channels in the respective layer. The convolution operation can be formulated as:  $y = b + \sum_i \sum_j \sum_k (\mathbf{x}_{i,j,k} \cdot \mathbf{w}_{i,j,k})$ . Here, **x** is the input subset, **w** is the kernel weight matrix, and b is a scalar bias. These layers are used for feature extractions.

- *Fully Connected Layers:* In this layer, each neuron has weighted synaptic connections to all neurons in the previous layer. In other words, a fully connected layer treats its input as a 1-dimensional vector and generates a 1-dimensional vector as a result.

- *Pooling Layers:* These layers extract local information in each feature map by downsampling input feature maps. The two most popular pooling layers are *average pooling* and *max pooling*. These layers are commonly used to reduce the spatial dimensions of the feature maps and help the models achieve translation invariance.

- *Transposed Convolution Layers:* These layers are used to upsample the spatial dimensions of the input feature maps, which are typically employed in image segmentation and GANs. Transposed convolution is also known as deconvolution and fractionally strided convolution. Compared to convolutional layers, the forward operations in these layers are similar to a backward pass through convolution layers, and the backward pass through transposed convolution is similar to the forward pass in a convolutional layer.

- *Non-Linear Activation Function:* Non-linearity is necessary for DNNs as they increase the decision boundaries and approximation power of the models. Without non-linearity, stacked layers could be folded into a single layer. Currently, the most popular non-linear function in DNNs is the rectified linear unit (ReLU).

DNNs typically are based on floating-point precision and trained with backpropagation algorithm. Each training step involves two phases: forward and backward. In the forward phase, the network is used to perform inference on the input. Afterward, the partial gradients with respect to the loss are propagated back to each layer in the backward phase. These partial gradients are then used to update the network parameters using stochastic gradient descent rules. After the network is trained, it can be utilized in inference mode to evaluate each input. In all of the state-of-the-art DNN architectures, the biggest portion of the computational demands is required by the multiplier blocks utilized in the convolutional, deconvolution and fully connected layers. We discuss next previous efforts to reduce these computational complexities.

### 2.2 Hardware-Software Co-design of Deep Neural Networks

Recent interest in efficient, low-cost inference of DNNs has motivated a broad exploration of viable algorithmic solutions, hardware designs as well as the intersection of the two, namely hardware-software co-design. Often, these solutions take advantage of the errorresilient nature of DNNs by trading off small accuracy loss for potentially large saving in computational overheads. DNNs error tolerance originates from the inherently approximate nature of the applications as well as the training process of the models, where some of the induced errors can be compensated by re-learning and fine-tuning the parameters.

We first discuss some of the existing algorithmic-based approaches aimed at simplifying DNN overheads. One of the promising solutions proposed in several studies was condensing large, cumbersome DNN models to smaller networks [11, 39]. This approach proposed to train the student (smaller model) to mimic to the outputs of the teacher (larger model) by modifying the loss function to consist of two parts: the losses with respect to the true labels and the outputs from the teacher model. Both the large and small models are based on floating-point precision. Other algorithmic solutions include iterative pruning, which aims to remove unnecessary synaptic connections and hence, reduce the computational and storage overhead of the models [60]. Other works proposed more efficient convolutional operations such as Winograd convolution [57] and depth-wise separable convolution [44].

For hardware-software co-design solutions, many studies have focused on optimization of neural networks for effective implementations targeting both FPGAs [27, 31, 28] and custom hardware accelerators [53, 93, 26]. Other works have focused on the optimization of the core computational blocks [13, 27, 80]. For example, Farabet *et al.* [27] propose the use of one hardware convolutional operator for implementing the filtering computation while the rest of the computation is done in software. Different parallelism and locality opportunities are also explored in recent work [80, 13, 12]. As an example, Chakradhar *et al.* [13] take advantage of inter-output and intra-output parallelism and design a dynamically configurable hardware design for the forward phase. A tile-based hardware accelerator that uses custom-designed memory structures to exploit data locality is proposed in DianNao [15] and is capable of performing 452 GOPs per second. Park *et al.* [69] proposed a "Big/Little" implementation, where two networks are trained and used to reduce energy requirements. For each input, the little network is first evaluated and the big network is triggered only if the result of the little network is not deemed confident enough. Targeting an FPGA platform, Zhang *et al.* [99] use a rooftop model to identify the best solution given a specific set of resources, thereby mitigating the under-utilization of memory bandwidth and computational logic. Their proposed tile-based custom design can achieve up to 61.62 GFLOPS using floating-point arithmetic.

To simplify the designs of hardware running DNNs, a number of recent works advocate the use of approximating computing techniques in the co-design solutions. Du *et al.* [25] propose the use of an approximate multiplier design for weight and input multiplication and conduct a broad design space exploration to determine the best network designs. Sarwar *et al.* propose a multiplier-less neural network where an accurate multiplier is replaced with an alphabet set multiplier to save power [81]. This work, however, focuses on multi-layer perceptrons and deep neural networks are not evaluated. Venkataramani *et al.* propose a methodology in which less sensitive neurons are approximated with precision scaling [96]. The power and accuracy results are then evaluated on a customized quality configurable neuromorphic processing engine to report the benefits. In a similar approach, Zhang *et al.* propose to remove the less critical neurons in favor of energy reduction [99].

Alternatively, DNNs with low precision data formats have enormous potentials for

reducing hardware complexity, power and latency. Not surprisingly, there exists a rich body of literature which studies such limited precisions. Previous work in this area have considered a wide range of reduced precision including fixed point [17, 33, 87], ternary (-1,0,1) [46] and binary (-1,1) [45, 84]. Chen *et al.* proposed Eyeriss, a spatial architecture along with a dataflow aimed at minimizing the movement energy overhead using data reuse [16]. For their implementation, a 16-bit fixed-point precision is utilized. Sankaradas *et al.* empirically determine an acceptable precision for their application [80] and reduce the precision to 16-bit fixed-point for inputs and intermediate values while maintaining 20-bit precision for weights. Chakradhar *et al.* propose a configurable co-processor where input and output values are represented using 16 bits while intermediate values use 48 bits [13]. Furthermore, comprehensive studies of the effects of different precision on deep neural networks are also available. Gysel *et al.* [34] propose Ristretto, a hardware-oriented tool capable of simulating a wide range of signal precisions. While they consider dynamic fixed-point, in their work the focus is on network accuracy, and thus, the hardware metrics are not evaluated.

### Chapter 3

# Hardware-Software Co-design of Deep Neural Network Accelerators

### 3.1 Introduction

One major challenge in designing DNN accelerators originates from the high-precision representation used for the network parameters and data paths. Typically, single precision (32-bit) floating-point format is used to implement state-of-the-art DNNs, which leads to large memory traffic and capacity requirements for both the network parameters and the intermediate computations. In addition, operations on high precision representations require expensive hardware multipliers and adders, which translates to large power and chip area.

In this chapter, our goal is to devise lightweight approximate accelerators for DNN accelerations that use fewer hardware resources with negligible reduction in accuracy performance. In order to simplify the hardware requirements, we co-design the DNN data representations by performing a detailed analysis of a broad spectrum of precision formats ranging from fixed-point, dynamic fixed point, powers-of-two to binary data precision. The powers-of-two and binary are particularly attractive as they eliminate the need for multipliers altogether, which provide a larger reduction in hardware requirements. In conjunction, we propose new training methods to compensate for accuracy loss due to the simpler representations. To boost the accuracy of the proposed lightweight accelerators, we describe ensemble processing techniques that use an ensemble of light-weight DNN accelerators to achieve the same or better accuracy than the original floating-point accelerator, while still using much fewer hardware resources. Using 65 nm technology libraries and industrial-strength design flow, we demonstrate a custom hardware accelerator design and training procedure which achieve low-power, low-latency while incurring insignificant accuracy degradation. We evaluate our design and technique on the CIFAR-10 and ImageNet datasets and show that significant reduction in power and inference latency is realized. Our work, as presented in this chapter, has been published in [36, 89, 92].

The organization for the rest of this chapter is as follows. In Section 3.2, we describe the various options for data precision in DNNs, and in Section 3.3, we provide various accelerators designs that are targeted for the precision of the DNN. Next, in Section 3.4, we provide our training methodology for low-precision DNNs, and in Section 3.5 we describe ensemble processing techniques to boost the accuracy of DNNs. Using the proposed methodologies and our custom accelerators, we discuss the results in Section 3.6. Finally, in Section 3.7 we provide the main conclusions of this chapter.

# **3.2 Data Precision Options**

In this chapter, we evaluate quantizations of parameters and intermediate signals to a variety of numerical representation formats with different precisions and ranges, from floatingpoint (32-bit single precision) to binary format (-1, 1) with several other points in between. We summarize the representations below:

**Floating-Point Format:** Readily available in most processing systems, this precision format is the most commonly employed among all DNNs producing many state-of-the-art results. However, arithmetic operations for floating-point data necessitate complicated circuitries for the computational units such as adders and multipliers as well as other logic. In addition, the large bit-width also requires ample memory bandwidths and capacity. As a result, this representation format is unsuitable for deployment on low-power and embedded systems.